# **User's Guide**

# 3P

# **Mezzanine Board**

# Three-port multirate interface for use with an EDT main board

Doc. 008-04026-01

Rev. 2013 December 19

EDT<sup>TM</sup> and Engineering Design Team<sup>TM</sup> are trademarks of Engineering Design Team, Inc. All other trademarks, service marks, and copyrights are the property of their respective owners<sup>†</sup>.

© 1997-2013 Engineering Design Team, Inc. All rights reserved.

International Distributors

Sky Blue Microsystems GmbH Geisenhausenerstr. 18 81379 Munich, Germany +49 89 780 2970, info@skyblue.de www.skyblue.de

In Great Britain:

Zerif Technologies Ltd.

Winnington House, 2 Woodberry Grove

Finchley, London N12 0DR

+44 115 855 7883, info@zerif.co.uk

www.zerif.co.uk

EDT, Inc. 2

3P User's Guide

#### **Terms of Use Agreement**

**Definitions.** This agreement, between Engineering Design Team, Inc. ("Seller") and the user or distributor ("Buyer"), covers the use and distribution of the following items provided by Seller: a) the binary and all provided source code for any and all device drivers, software libraries, utilities, and example applications (collectively, "Software"); b) the binary and all provided source code for any and all configurable or programmable devices (collectively, "Firmware"); and c) the computer boards and all other physical components (collectively, "Hardware"). Software, Firmware, and Hardware are collectively referred to as "Products." This agreement also covers Seller's published Limited Warranty ("Warranty") and all other published manuals and product information in physical, electronic, or any other form ("Documentation").

License. Seller grants Buyer the right to use or distribute Seller's Software and Firmware Products solely to enable Seller's Hardware Products. Seller's Software and Firmware must be used on the same computer as Seller's Hardware. Seller's Products and Documentation are furnished under, and may be used only in accordance with, the terms of this agreement. By using or distributing Seller's Products and Documentation, Buyer agrees to the terms of this agreement, as well as any additional agreements (such as a nondisclosure agreement) between Buyer and Seller.

**Export Restrictions.** Buyer will not permit Seller's Software, Firmware, or Hardware to be sent to, or used in, any other country except in compliance with applicable U.S. laws and regulations. For clarification or advice on such laws and regulations, Buyer should contact: **U.S. Department of Commerce, Export Division, Washington, D.C., U.S.A.**

Limitation of Rights. Seller grants Buyer a royalty-free right to modify, reproduce, and distribute executable files using the Seller's Software and Firmware, provided that: a) the source code and executable files will be used only with Seller's Hardware; b) Buyer agrees to indemnify, hold harmless, and defend Seller from and against any claims or lawsuits, including attorneys' fees, that arise or result from the use or distribution of Buyer's products containing Seller's Products. Seller's Hardware may not be copied or recreated in any form or by any means without Seller's express written consent.

**No Liability for Consequential Damages.** In no event will Seller, its directors, officers, employees, or agents be liable to Buyer for any consequential, incidental, or indirect damages (including damages for business interruptions, loss of business profits or information, and the like) arising out of the use or inability to use the Products, even if Seller has been advised of the possibility of such damages. Because some jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to Buyer. Seller's liability to Buyer for actual damages for any cause whatsoever, and regardless of the form of the action (whether in contract, product liability, tort including negligence, or otherwise), will be limited to fifty U.S. dollars (\$50.00).

Limited Hardware Warranty. Seller warrants that the Hardware it manufactures and sells shall be free of defects in materials and workmanship for a period of 12 months from date of shipment to initial Buyer. This warranty does not apply to any product that is misused, abused, repaired, or otherwise modified by Buyer or others. Seller's sole obligation for breach of this warranty shall be to repair or replace (F.O.B. Seller's plant, Beaverton, Oregon, U.S.A.) any goods that are found to be non-conforming or defective as specified by Buyer within 30 days of discovery of any defect. Buyer shall bear all installation and transportation expenses, and all other incidental expenses and damages.

Limitation of Liability. In no event shall Seller be liable for any type of special consequential, incidental, or penal damages, whether such damages arise from, or are a result of, breach of contract, warranty, tort (including negligence), strict liability, or otherwise. All references to damages herein shall include, but not be limited to: loss of profit or revenue; loss of use of the goods or associated equipment; costs of substitute goods, equipment, or facilities; downtime costs; or claims for damages. Seller shall not be liable for any loss, claim, expense, or damage caused by, contributed to, or arising out of the acts or omissions of Buyer, whether negligent or otherwise.

**No Other Warranties.** Seller makes no other warranties, express or implied, including without limitation the implied warranties of merchantability and fitness for a particular purpose, regarding Seller's Products or Documentation. Seller does not warrant, guarantee, or make any representations regarding the use or the results of the use of the Products or Documentation or their correctness, accuracy, reliability, currentness, or otherwise. All risk related to the results and performance of the Products and Documentation is assumed by Buyer. The exclusion of implied warranties is not permitted by some jurisdictions. The above exclusion may not apply to Buyer.

**Disclaimer.** Seller's Products and Documentation, including this document, are subject to change without notice. Documentation does not represent a commitment from Seller.

EDT, Inc.

# **Contents**

| 3P Mezzanine Board                                       | c  |

|----------------------------------------------------------|----|

| Overview                                                 | Ç  |

| FPGAs: Mezzanine Board + Main Board                      |    |

| Related Resources                                        | 11 |

| Installation and the EDT Installation Package            |    |

| The PCD Device Driver                                    |    |

| Firmware: FPGA Configuration (.bit) Files                |    |

| Applications and Utilities                               |    |

| Building or Rebuilding an Application                    |    |

| OCXSnap and OCXPlay                                      |    |

| Configuring the 3P: Initialization and Setup             | 16 |

| Initializing the Board and Preparing for DMA             |    |

| Configuring the FPGAs                                    |    |

| Initializing the Clock Signals and Logic Circuits        |    |

| Initializing the Memory                                  |    |

| Enabling and Verifying the Input Signals – Ports 1 and 2 |    |

| Initializing and Enabling the Data Paths                 | 20 |

| Querying the SFP/+ Transceivers                          |    |

| Time Code                                                | 20 |

| Framing                                                  | 20 |

| OTN and OC / STM                                         | 21 |

| 10 GbE                                                   | 21 |

| Basic Self-Testing                                       | 22 |

| Board Architecture                                       |    |

|                                                          |    |

| ADDENDIV A                                               |    |

| APPENDIX A:  Main Board UI FPGA Configuration File       | 25 |

| · ·                                                      |    |

| Overview                                                 |    |

| threep.bit                                               |    |

| 0x00–0x7F Main Board                                     |    |

| 0x00 Command                                             |    |

| 0x03 Interrupt Status                                    |    |

| 0x04 Interrupt Enable                                    |    |

| 0x05 FPGA Configuration File Organization                |    |

| 0x06 PLL Status<br>0x0F Configuration                    |    |

| 0x10–11 DMA Channel Enable                               |    |

| 0x12–13 DMA Channel Direction [Reserved]                 |    |

| 0x14–15 DMA Channel Edge [Reserved]                      |    |

| 0x16 Least Significant Bit First                         |    |

| 0x18–19 Underflow                                        |    |

| 0x1A-1B Overflow                                         |    |

| 0x40-43 Mezzload                                         |    |

| 0x44 Mezzload Control / Select                           |    |

| 0x4A Port 2 DMA Transmit Mode                            |    |

| 0x60-62 Extended Indirect Register Address               |    |

| 0x63 Extended Indirect Register Data                     |    |

| 0x65 Serial Master Interface Status                      |    |

| 0x66 Serial Master Interface Read [7–0]                  |    |

| 0x67 Serial Master Interface Register Address            |    |

| 0x68 Serial Master Interface Write                       | 30 |

| 0x69 Serial Master Interface Read [15–8]                |                                         |

|---------------------------------------------------------|-----------------------------------------|

| 0x7C–7D FPGA Configuration File Design ID               |                                         |

| 0x7E FPGA Configuration File Version String             |                                         |

| 0x7F Board ID                                           | 32                                      |

|                                                         |                                         |

| APPENDIX B:                                             |                                         |

| Mezzanine Board FPGA Configuration Files                | 33                                      |

| Overview                                                |                                         |

|                                                         |                                         |

| threep_10g_sdh_sdh.bit - Standard Registers             |                                         |

| 0x00-7F [See threep.bit]                                |                                         |

| 0x80–9F Port 0                                          |                                         |

| 0x81 Port 0 LIU Status                                  |                                         |

| 0x83 Port 0 Transceiver                                 |                                         |

| 0x84 Port 0 Enable                                      |                                         |

| 0x85 Port 0 Receive Framing Control                     |                                         |

| 0x86 Port 0 Receive Filter Control                      |                                         |

| 0x89 Port 0 Output Data Select                          |                                         |

| 0x8B Port 0 Frame Statistics Count Control              |                                         |

| 0x8C Port 0 Link Fault Status                           |                                         |

| 0x8D Port 0 Loopback                                    |                                         |

| 0x8E Port 0 PCS Control                                 |                                         |

| 0xA0–BF Port 1                                          |                                         |

| 0xA0 Port 1 Configuration 0                             |                                         |

| 0xA1 Port 1 Configuration 1                             |                                         |

| 0xA2 Port 1 Status                                      |                                         |

| 0xA3-A4 Port 1 [See 0x83-84]                            |                                         |

| 0xA5 Port 1 Receive Framing Control                     |                                         |

| 0xA6 Port 1 Receive Filter Control                      |                                         |

| 0xA7 Port 1 Receive Status                              |                                         |

| 0xA8 Port 1 Receive Frame Status                        |                                         |

| 0xA9 Port 1 Transmit Framing Configuration              |                                         |

| 0xAA Port 1 Transmit Status                             |                                         |

| 0xAB Port 1 [See 0x8B]                                  |                                         |

| 0xAC Port 1 B1 Error Mask                               |                                         |

| 0xAE Port 1 Receive Synchronization Control             |                                         |

| 0xAF Port 1 Transmit Synchronization Control [Reserved] |                                         |

| 0xC0-DF Port 2 [See 0xA0-BF]                            |                                         |

| 0xE0–FF Not Port-Specific                               |                                         |

| 0xE0 Mezzanine FPGA Configuration File Version String   |                                         |

| 0xE1 Mezzanine FPGA Configuration File Organization     | 43                                      |

| 0xE2–E3 Mezzanine FPGA Configuration File Design ID     | 43                                      |

| 0xE4–E6 DDR2 Bank Status and Control                    |                                         |

| 0xE7 Serial Master Interface Status                     |                                         |

| 0xE8 Serial Master Interface Read                       |                                         |

| 0xE9 Serial Master Interface Register Address           |                                         |

| 0xEA Serial Master Interface Write                      |                                         |

| 0xEB–ED Time Distribution                               | • • • • • • • • • • • • • • • • • • • • |

| 0xEE PRBS Mode                                          | • • • • • • • • • • • • • • • • • • • • |

| 0xF4 Frequency Counter Control                          |                                         |

| 0xF5–F7 Frequency Counter Value                         |                                         |

| threep_10g_sdh_sdh.bit - Extended Registers             | 47                                      |

| 0x800000–FF Port 0                                      |                                         |

| 0x800005 Port 0 Bit Error Rate Count                    |                                         |

| 0x800006 Port 0 64B / 66B Decode Error Count            |                                         |

| 0x800008–09 Port 0 Local Link Fault Count               | 47                                      |

| 0x80000A-0B Port 0 Remote Link Fault Count              |                                         |

| 0x800100-FF Port 1                                      | 48                                      |

| 0x800100 Port 1 Transmit National Byte        | 48                     |

|-----------------------------------------------|------------------------|

| 0x800101-04 Port 1 Transmit Test Data         | 48                     |

| 0x800105-07 Port 1 B1 Error Count             | 48                     |

| 0x800108-0B Port 1 B2 Error Count             | 48                     |

| 0x80010C-0E Port 1 M1 Error Count             | 49                     |

| 0x80010F-10 Port 1 Loss of Frame Count        | 49                     |

| 0x800111-12 Port 1 Frame Pattern Error Count  | 49                     |

|                                               | 50                     |

| 0x800115 Port 1 Demux Bitmap                  | 51                     |

| 0x800116 Port 1 Demux Bitmap Readback         | 52                     |

|                                               | 52                     |

| threep_10g_emac_emac.bit – Standard Registers |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               | 54                     |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               | 57                     |

|                                               |                        |

|                                               | 57                     |

|                                               | Oriver Swing Control58 |

|                                               |                        |

|                                               | 58                     |

|                                               | 58                     |

|                                               |                        |

| · ·                                           |                        |

|                                               | 59                     |

|                                               | 59                     |

|                                               | 59                     |

|                                               | 59                     |

|                                               | ring59                 |

|                                               | on60                   |

|                                               | n ID60                 |

| 0xE4–E6 DDR2 Bank Status and Control          | 60                     |

|                                               | 61                     |

| 0xE8 Serial Master Interface Read             | 61                     |

| 0xE9 Serial Master Interface Register Address | 61                     |

| •                                             | 61                     |

| 0xEB-ED Time Distribution                     | 62                     |

| 0xEE PRBS Mode                                | 62                     |

|                                               | 62                     |

|                                               | 62                     |

| threep_10g_emac_emac.bit - Extended Registers |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               |                        |

|                                               | 64                     |

| •                                             | 64                     |

|                                               |                        |

| threep_stm64_sdh_sdh.bit – Standard Registers           |                                         |

|---------------------------------------------------------|-----------------------------------------|

| 0x00-7F [See threep.bit]                                |                                         |

| 0x80–9F Port 0                                          |                                         |

| 0x81 Port 0 LIU Status                                  |                                         |

| 0x83 Port 0 Transceiver                                 |                                         |

| 0x84 Port 0 Enable                                      |                                         |

| 0x85 Port 0 Receive Framing Control                     | 66                                      |

| 0x86 Port 0 Receive Filter Control                      |                                         |

| 0x89 Port 0 Output Data Control                         |                                         |

| 0x8B Port 0 Frame Statistics Count Control              |                                         |

| 0x8C Port 0 B1 Error Mask                               |                                         |

| 0x8D Port 0 Frame Tagging                               | 68                                      |

| 0x8E Port 0 Receive Synchronization Control             |                                         |

| 0x8F Port 0 Transmit Synchronization Control [Reserved] | 68                                      |

| 0x90 Port 0 [Reserved]                                  | 68                                      |

| 0x91 Port 1 Framer Rate Select                          |                                         |

| 0xA0-BF Port 1                                          | 69                                      |

| 0xA0 Port 1 Configuration 0                             | 69                                      |

| 0xA1 Port 1 Configuration 1                             |                                         |

| 0xA2 Port 1 Status                                      |                                         |

| 0xA3-A4 Port 1 [See 0x83-84]                            |                                         |

| 0xA5 Port 1 Receive Framing Control                     |                                         |

| 0xA6 Port 1 Receive Filter Control                      |                                         |

| 0xA7 Port 1 Receive Status                              |                                         |

| 0xA8 Port 1 Receive Frame Status                        |                                         |

| 0xA9 Port 1 Transmit Framing Configuration              |                                         |

| 0xAA Port 1 Transmit Status                             |                                         |

| 0xAB Port 1 [See 0x8B]                                  |                                         |

| 0xAC Port 1 B1 Error Mask                               |                                         |

| 0xAE Port 1 Receive Synchronization Control             |                                         |

| 0xAF Port 1 Transmit Synchronization Control [Reserved] |                                         |

| 0xB0–BF Port 1 [Reserved]                               |                                         |

| 0xC0-DF Port 2 [See 0xA0-BF]                            |                                         |

| 0xE0-FF Not Port-Specific                               |                                         |

| 0xE0 Mezzanine FPGA Configuration File Version String   |                                         |

| 0xE1 Mezzanine FPGA Configuration File Organization     |                                         |

| 0xE2–E3 Mezzanine FPGA Configuration File Design ID     |                                         |

| 0xE4–E6 DDR2 Bank Status and Control                    |                                         |

| 0xE7 Serial Master Interface Status                     |                                         |

| 0xE8 Serial Master Interface Read                       |                                         |

| 0xE9 Serial Master Interface Register Address           |                                         |

| 0xEA Serial Master Interface Write                      |                                         |

| 0xEB-ED Time Distribution                               |                                         |

| 0xEE PRBS Mode                                          | • • • • • • • • • • • • • • • • • • • • |

| 0xF4 Frequency Counter Control                          |                                         |

| 0xF5–F7 Frequency Counter Value                         |                                         |

|                                                         |                                         |

| threep_stm64_sdh_sdh_bit – Extended Registers           |                                         |

| 0x800000–FF Port 0                                      |                                         |

| 0x800001–02 Port 0 Transmit Test Pattern                |                                         |

| 0x800005–07 Port 0 B1 Error Count                       |                                         |

| 0x800008–0B Port 0 B2 Error Count                       |                                         |

| 0x80000C-0E Port 0 M1 Error Count                       |                                         |

| 0x80000F–10 Port 0 Loss of Frame Count                  |                                         |

| 0x800011–12 Port 0 Frame Pattern Error Count            |                                         |

| 0x800013–14 Port 0 False Frame Count                    |                                         |

| 0x800015–17 Port 0 Demux Bitmask                        |                                         |

| 0x800018–19 Port 0 Demux Bitmask Readback               |                                         |

| 0x800100–FF Port 1                                      | 81                                      |

| 0x800100 Port 1 Transmit National Byte                  | 81 |

|---------------------------------------------------------|----|

| 0x800101–04 Port 1 Transmit Test Data                   |    |

| 0x800105-14 Port 1 [See 0x800005-14 Port 0]             | 81 |

| 0x800115 Port 1 Demux Bitmap                            | 82 |

| 0x800116 Port 1 Demux Bitmap Readback                   |    |

| 0x800200-FF Port 2 [See 0x800100-FF]                    | 83 |

| threep_sdh_sdh_sync.bit – Standard Registers            |    |

| 0x00-7F [See threep.bit]                                |    |

| 0x80–9F Port 0                                          |    |

| 0x80–9F Port 0 [Reserved]                               |    |

| 0x8F Port 0 Transmit Synchronization Control            |    |

|                                                         |    |

| 0x90-9F Port 0 [Reserved]                               |    |

| 0xA0_BF Port 1                                          |    |

| 0xA0 Port 1 Configuration 0                             |    |

| 0xA1 Port 1 Configuration 1                             |    |

| 0xA2 Port 1 Status                                      |    |

| 0xA3-A4 Port 1 [See 0x83-84]                            |    |

| 0xA5 Port 1 Receive Framing Control                     |    |

| 0xA6 Port 1 Receive Filter Control                      |    |

| 0xA7 Port 1 Receive Status                              |    |

| 0xA8 Port 1 Receive Frame Status                        |    |

| 0xA9 Port 1 Transmit Framing Configuration              |    |

| 0xAA Port 1 Transmit Status                             |    |

| 0xAB Port 1 [See 0x8B]                                  |    |

| 0xAC Port 1 B1 Error Mask                               |    |

| 0xAE Port 1 Receive Synchronization Control             |    |

| 0xAF Port 1 Transmit Synchronization Control [Reserved] |    |

| 0xC0-DF Port 2 [See 0xA0-BF]                            |    |

| 0xE0-FF Not Port-Specific                               |    |

| 0xE0 Mezzanine FPGA Configuration File Version String   |    |

| 0xE1 Mezzanine FPGA Configuration File Organization     |    |

| 0xE2–E3 Mezzanine FPGA Configuration File Design ID     | 90 |

| 0xE4–E6 DDR2 Bank Status and Control                    |    |

| 0xE7 Serial Master Interface Status                     |    |

| 0xE8 Serial Master Interface Read                       |    |

| 0xE9 Serial Master Interface Register Address           |    |

| 0xEA Serial Master Interface Write                      |    |

| 0xEB–ED Time Distribution                               |    |

| 0xEE PRBS Mode                                          |    |

| 0xF4 Frequency Counter Control                          |    |

| 0xF5–F7 Frequency Counter Value                         |    |

| threep_sdh_sdh_sync.bit – Extended Registers            |    |

| 0x800000–FF Port 0 [Reserved]                           | 94 |

| 0x800100–FF Port 1                                      |    |

| 0x800100 Port 1 Transmit National Byte                  | 94 |

| 0x800101–04 Port 1 Transmit Test Data                   | 94 |

| 0x800105–07 Port 1 B1 Error Count                       | 94 |

| 0x800108-0B Port 1 B2 Error Count                       | 95 |

| 0x80010C-0E Port 1 M1 Error Count                       |    |

| 0x80010F-10 Port 1 Loss of Frame Count                  |    |

| 0x800111–12 Port 1 Frame Pattern Error Count            | 95 |

| 0x800113-14 Port 1 False Frame Count                    | 96 |

| 0x800115 Port 1 Demux Bitmap                            |    |

| 0x800116 Port 1 Demux Bitmap Readback                   | 98 |

| 0x800200–FF Port 2                                      |    |

| 0x800200-16 Port 2 [See 0x800100-16 Port 1]             | 98 |

|                                                         |    |

# 3P Mezzanine Board

# **Overview**

The 3P is a three-port mezzanine board that provides receive-and-transmit capability for these data formats:

- 10GbE (optical only);

- 1GbE (electrical or optical);

- Serial data:

- Optical transport network (OTN); or

- SONET / SDH (OC3 / STM1 through OC192 / STM64).

#### NOTE

In this guide, the signal names SONET (OC3/12/48) and SDH (STM1/4/16) are used interchangeably. For signal standards, see Related Resources on page 11.

Features on the 3P include:

- Three independent blocks of DDR2 DRAM (two can be combined to make a larger block);

- Three programmable oscillators (one per port);

- Three optional small form pluggables (SFP/+ denotes either an SFP or an SFP+) one per port;

- Three optional SFP/+ line interface units (LIUs)...

- Port 0 = 10G LIU (external) or MGT (on the FPGA);

- Port 1 = SDH LIU (external) or MGT (on the FPGA);

- Port 2 = SDH LIU (external) or MGT (on the FPGA).

Table 1 shows the defaults and options for each port; other options may be available upon request. For details and illustrations, see Board Architecture on page 23.

Table 1. Options by Port – LIU, Signal, Wavelength, and Module (SFP/+)

| Port | LIU                   | Signal*                                                  | Wavelength                        | Module |  |

|------|-----------------------|----------------------------------------------------------|-----------------------------------|--------|--|

| 0    | 10G                   | 10GbE (10G Base-R), OTN, or OC192 (STM64)                | 850 / 1310 nm                     | SFP+   |  |

|      | MGT                   | 1GbE (1000 Base-X or -T) or serial data                  | Electrical / 850 / 1310 / 1550 nm | SFP    |  |

| 1    | SDH                   | 1 GbE (1000 Base-X or -T), OTN, or OC3/12/48 (STM1/4/16) | Electrical / 850 / 1310 / 1550 nm | SFP    |  |

|      | MGT                   | 1GbE (1000 Base-X or -T) or serial data                  | Electrical / 850 / 1310 / 1550 nm | SFP    |  |

| 2    | [Identical to port 1] |                                                          |                                   |        |  |

|      |                       |                                                          |                                   |        |  |

<sup>\*</sup> For details on these standards and parts, see Related Resources on page 11.

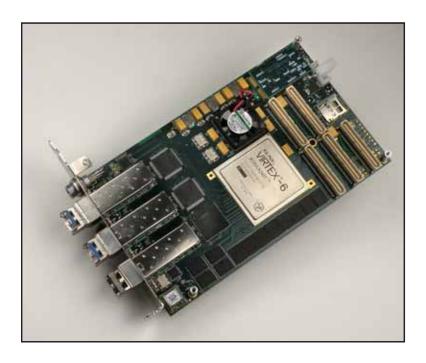

The 3P is paired with a PCIe main board for high-speed DMA and other resources. Together, the two boards provide the field-programmable gate arrays (FPGAs) shown below.

3P Mezzanine Board Overview

# FPGAs: Mezzanine Board + Main Board

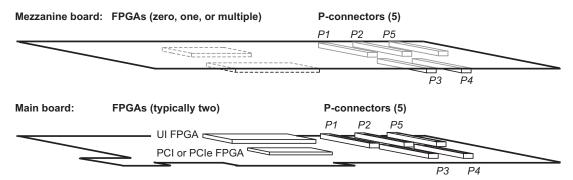

In general, an EDT board pair can have several FPGAs, as shown in Figure 1.

Figure 1. Generic EDT Board Pair

Not to scale. Generic representations only; actual boards may vary.

In specific, your 3P board pair has the following FPGAs.

- The 3P mezzanine board has one user-programmable FPGA, called the *3P FPGA*. For loading instructions, see Configuring the 3P: Initialization and Setup on page 16.

- The PCIe main board has two FPGAs:

- The *user interface (UI) FPGA* links the 3P FPGA to the main board's PCI or PCIe FPGA. Loading details are in the PCIe Main Board User's Guide (see Related Resources on page 11).

- The PCIe FPGA communicates with the host computer over the PCIe bus and implements the DMA engine, which transfers data between the board and the host. This FPGA loads automatically, at powerup, with the correct firmware from the main board's FPGA configuration flash memory.

These FPGAs will be discussed in more detail throughout the rest of this guide.

3P Mezzanine Board Overview

# **Related Resources**

The resources and documentation below may be helpful or necessary for your applications.

#### **EDT Resources**

- SFP (1310)

- SFP (1550)

oscillator (XO)

• Programmable crystal Si570

FTLF1321P1BTL

FTLF1521P1BCL

|                   | Description                                                      |                                             | Detail                               | URL                             |

|-------------------|------------------------------------------------------------------|---------------------------------------------|--------------------------------------|---------------------------------|

| 3P specifications |                                                                  |                                             | Datasheet                            | www.edt.com [find product page] |

|                   | <ul> <li>PCIe8 LX/SX/FX docum</li> </ul>                         | entation                                    | Datasheet & user's guide             | 11                              |

|                   | Time Distribution docum                                          | nentation                                   | User's guide                         | 11                              |

|                   | Application Programmin                                           | g Interface                                 | HTML and PDF                         | www.edt.com/api                 |

|                   | <ul> <li>Installation packages (V</li> </ul>                     | Vindows)                                    | Driver software & firmware downloads | www.edt.com/software.html       |

|                   | Standards                                                        |                                             |                                      |                                 |

|                   | Description                                                      | Pertains to                                 | Documentation                        | URL                             |

|                   | <ul> <li>International Telecommunications Union (ITU)</li> </ul> | Optical Transport<br>Network (OTN)          | G.709/Y.1331 03/2003                 | www.itu.int                     |

|                   | • IEEE                                                           | Ethernet framing                            | IEEE 802-3                           | www.ieee802.org/3/              |

|                   | Parts                                                            |                                             |                                      |                                 |

|                   | Description                                                      | Part Number                                 | Manufacturer                         | URL                             |

|                   | 3P FPGA - Virtex 6                                               | XC6VLX240T,<br>LX365T, SX315T, or<br>SX47ST | Xilinx                               | www.xilinx.com                  |

|                   | <ul> <li>Line interface units<br/>(LIUs) – external:</li> </ul>  |                                             |                                      |                                 |

|                   | – 10G                                                            | S19250                                      | Applied Micro                        | www.appliedmicro.com            |

|                   | - SDH                                                            | SLK2511                                     | Texas Instruments                    | www-s.ti.com/sc/ds/slk2511.pdf  |

|                   | <ul><li>SFP/+ modules (nm):</li></ul>                            |                                             |                                      |                                 |

|                   | - SFP+ (850)                                                     | FTLX8571D3BCL                               | Finisar                              | www.finisar.com                 |

|                   | - SFP+ (1310 / 1550)                                             | FTLX1371D3BCL                               | "                                    | u                               |

|                   | <ul><li>SFP (electrical)</li></ul>                               | FCMJ85213                                   | "                                    | "                               |

|                   | - SFP (850)                                                      | FTLF8524P2WNV                               | ű                                    | "                               |

|                   |                                                                  |                                             |                                      |                                 |

Silicon Labs

www.silabs.com

# Installation and the EDT Installation Package

To physically install the 3P, follow the steps below while referring to Figure 3 on page 23.

- 1. Power off your system; EDT recommends doing so before removing or replacing any transceiver, despite manufacturers' claims that transceivers are hot-swappable.

- 2. Using static-dissipative precautions, remove the board pair from its shipping packaging.

- 3. Make a note of the position of each SFP/+ on the 3P mezzanine board (they can be different, so you'll need to remember which one goes where).

- 4. Remove the SFP/+s to enable the board pair to fit into the host system.

- 5. Insert the board pair into the host system.

- 6. Working through the back panel on the host system, place each SFP/+ back into its original position.

- 7. Review the EDT installation package resources. as explained in the rest of this section.

**NOTE**

For a link to the latest installation packages, see Related Resources on page 11. For new installations, use the latest package; for existing applications, upgrade only if you have a specific reason to do so.

### The PCD Device Driver

Your EDT installation package contains the PCD device driver – the software that runs on the host computer and allows it to communicate with your EDT product. The driver is loaded into the kernel upon installation and runs as a kernel module. The driver name and subdirectory is specific to your operating system, and the installation script automatically installs the correct driver in the correct manner.

# Firmware: FPGA Configuration (.bit) Files

Included in your EDT installation package, as shown in Table 2 on page 13, are firmware files, also called FPGA configuration (.bit) files. Each firmware file is FPGA-specific and interface-specific, so each FPGA must be loaded with the correct one. For the PCIe FPGA, EDT preloads the correct file, which is implemented automatically at system power-on by nonvolatile (flash) memory; however, other FPGAs must be loaded by the user.

For specific details on loading the firmware, see Configuring the 3P: Initialization and Setup on page 16.

**NOTE** In addition to the firmware files listed in this user's guide, custom firmware files may be requested.

#### Table 2. Firmware (.bit) files

| To see firmware for  | look in this subdirectory | for file(s) named        | loaded in this way      |

|----------------------|---------------------------|--------------------------|-------------------------|

| Main board PCIe FPGA | flash/FPGApart#           | [n/a; file is preloaded] | Automatically, by flash |

| Main board UI FPGA   | bitfiles/FPGApart#        | threep.bit               | Manually, by user       |

| Mezzanine board FPGA | bitfiles/FPGApart#        | [see list below*]        | Manually, by user       |

<sup>\*</sup> In the mezzanine board subdirectory, you'll find these files...

threep\_10g\_sdh\_sdh.bit If all three ports have SDH LIUs, this file configures the 3P FPGA thus:

Port 0 = 10G Base-R

Port 1 = OC3/12/48 (STM1/4/16) Port 2 = OC3/12/48 (STM1/4/16)

threep\_10g\_emac\_emac\_bit If port 0 has a 10G LIU, and ports 1 and 2 have MGTs, this file configures

the 3P FPGA thus: Port 0 = 10G Base-R Port 1 = 1GbE (via MGT) Port 2 = 1GbE (via MGT)

threep\_stm64\_sdh\_sdh.bit If all three ports have SDH LIUs, this file configures the 3P FPGA thus:

Port 0 = OC192 (STM64)

Port 1 = OC3/12/48 (STM1/4/16) Port 2 = OC3/12/48 (STM1/4/16)

threep\_sdh\_sdh\_sync.bit If ports 1 and 2 have SDH LIUs, this file configures the 3P FPGA thus:

Port 0 = not used

Port 1 = OC3/12/48 (STM1/4/16) Port 2 = OC3/12/48 (STM1/4/16)

# **Applications and Utilities**

In addition to the above resources, the EDT installation package includes application and utility files that you can use to initialize and configure the board, access the registers, and perform basic self-testing. In many cases, C or C++ source is provided so you can use the files as starting points to write your own applications. The most commonly useful files are described below; for a complete list, see the README file.

These 3P files are in the top-level directory of your EDT installation package...

lib\_threep.c C library routines that you can use in your 3P applications.

edt\_threep.h Include file for the above C library routines.

threep\_setup Utility application that configures the LIU on port 0 and sets up each port's

reference clock.

threep\_setup.c C source for threep\_setup.

In addition, the 3P is supported by C++ files in the subdirectory liboax. The below resources are in the C++ library at liboax.lib (for Windows) or liboax.so (for Linux).

OCXSnap Example application that captures data from the 3P board and transfers it to disk

for testing or verification.

OCXSnap.cpp C++ source for OCXSnap.

OCXPlay Example application that outputs the data captured by OCXSnap from the disk for

testing or verification.

OCXPlay.cpp C++ source for OCXPlay.

ReadXFPSFP Example application that queries the state of the transceiver modules. For details,

see Initializing and Enabling the Data Paths on page 20.

ReadXFPSFP.cpp C++ source for ReadXFPSFP.

### **Sample Applications**

simple\_getdata Serves as an example of a variety of DMA-related operations, including reading the

data from the connector interface and writing it to a file, as well as measuring input

rate.

simple\_putdata Serves as an example of a variety of DMA-related operations, including reading

data from a file and writing it out to the connector interface.

test\_timeout Under normal operation, timeouts cancel DMA transfers. This application

exemplifies giving notification when a timeout occurs, without canceling DMA.

### **Utilities**

pdb Enables interactive reading and writing of the UI FPGA registers.

timing\_test Programs the timecode microcontroller and tests the timecode input.

### **Basic Testing**

Various files (source, executables, and FPGA configuration files) are available to help you perform basic testing on your EDT board (see Basic Self-Testing on page 22). These files include at least...

sslooptest Verifies installation and basic functioning of most EDT PCIe boards. Determines

board model and runs appropriate loopback test.

# **Building or Rebuilding an Application**

In your EDT installation package, executable and PCD source files are in the top-level directory. Therefore, if you need to build or rebuild an application, run <code>make</code> in that directory.

Windows users must install a C compiler; EDT recommends the Microsoft Visual C compiler for Windows. Linux users can use the god compiler typically included with the Linux installation.

After you build or rebuild an application, use the --help command-line option for a list of usage options and descriptions.

# **OCXSnap and OCXPlay**

With their source code, the two command-line applications OCXSnap and OCMPlay provide an example of capturing data and playing it back. They can be invoked with various options for customization.

**NOTE**

C software on earlier EDT boards (e.g., OCM, OC192) invoked programs via DMA channel, with each DMA channel linked to a specific DMA direction and physical port on the board; however, the new liboax library uses an argument to specify which port. This change was needed because the 3P uses four DMA channels but has six possible port / direction combinations.

If possible, the software will use the specified clock speed to select the correct channel.

If not, you can specify which port by entering...

-P port#

...replacing port# with the desired port number.

For a Help message listing all usage options, invoke these applications with the flag -h. For example...

```

OCXSnap -h

```

The following example captures 2048 MB (2GB) of an OC3 / STM1 signal from port 1 (-P 1) by specifying a line rate of 1 (-r 1) for OC3 / STM1 and an output file size of 2048 MB (-s 2048)...

```

OCXSnap -P 1 -r 1 -s 2048 -o outputfilename

```

...where 1 represents the numeric digit "1" and outputfilename represents the name of the output file.

After about two minutes, when the application terminates, the companion invocation of OCXPlay outputs the captured data from port 1 at the OC3 / STM1 line rate, with input from the specified file...

```

OCXPlay -P 1 -r 1 -i inputfilename

```

...where 1 represents the numeric digit "1" and inputfilename represents the name of the input file.

The above example requires a host disk system that can read and write a file at 20 MB per second; the comparable run for OC12 / STM4 data requires a disk system that can function at 80 MB per second.

Below are a few considerations not provided in the Help message...

- The example application OCXSnap allows you to specify that the output be formatted in hexadecimal chunks of 32, 16, or 8 bits, using the flags -H, -Hw, or -HHb, respectively. In all cases, the most significant bit is the first bit output (in time) and the leftmost bit of the chunk (in memory).

- The flag -s to OCXSnap specifies the final file size in megabytes. The application will terminate when the specified size has been reached.

- The application OCXSnap allows you to change the default number and size of the ring buffers using the flags n and –b. For performance reasons, the ring buffer size is always rounded to the nearest multiple of 4096. The application then checks to determine whether the requested size and number of ring buffers is reasonable for the line rate. If it is not, the application configures the ring buffers as requested, but emits a warning message.

- Both OCXSnap and OCXPlay are designed to run basic initialization by default. If you want to skip basic initialization (for example, if another program has already performed it and you do not want to run it again), you can do so by using the -I initialization flag.

# Configuring the 3P: Initialization and Setup

In the libox library, the EDT board and its configuration are treated as two distinct entities: The board is an object derived from an abstract base class EdtoCX, while the configuration is an object of class EdtoCXCfg. The config class has built-in argument parsing to set its various options.

The example applications initialize the 3P by synchronizing the digital PLLs that produce the clock signals, initializing the port 0 memory (if any), enabling the LIUs, and enabling the data paths. If you are using the EDT example applications, this initialization happens automatically. If, however, you are writing your own application for the 3P, you will need to use the correct initialization sequence.

# Initializing the Board and Preparing for DMA

To open the board class derived from <code>Edtocx</code> you'll need to set up the configuration object. To do so, set up the member variables of this object in a command-line—based program by passing in to the <code>Edtocx::ParseOptions</code> function the <code>argc</code> and <code>argv</code> arguments passed into your <code>main()</code> function

The example below shows a way to create the EdtoCXCfg configuration object and parse arguments. The routine cfg.Init() sets the default flags and data rate for this program, all of which will be overwritten by options parsed by the routine cfg.ParseOptions().

```

EdtOCXCfg cfg;

EdtOCX *board;

```

#### Figure A. To set the default flags, the timeout in milliseconds, and the default line rate, enter...

```

cfg.Init(

EDT_OCX_FULL_INIT | EDT_OCX|FRAMED | EDT_OCX_ENABLE_MEM | EDT_OCX_SWAP, 1000,

STM16_RATE);

cfg.ParseOptions(argc, argv, true);

```

After the configuration is set, it can be used to open the correct mezzanine board...

```

board = EdtOCX::OpenBoard(&cfg, false);

```

Now the board can be initialized based on the values in the Edtocxcfg object.

For complete initialization, which will allow DMA to be enabled, run...

```

rc = Board->Configure(); // The value returned will be 0 for success, or -1 for failure.

// The Configure function will load the appropriate FPGA configuration files, set up

// the clocks, and synchronize with the input signal.

```

Board->SetupDma(); // This uses default values for buffer size based on effective data

// rate.

To verify the state of the signal after initialization, run...

```

Board->HasSignal();

Board->IsFramed();

To start DMA, run...

Board->ChannelStart(); // This will initiate the DMA.

```

# Configuring the FPGAs

EDT FPGA configuration includes some steps that are automatic, and some that must or may be done manually. The procedures in this section cover both automatic and manual (direct) board setup.

### **Unit number**

The first step in setting up each board pair is to determine its system-assigned unit number (by default, 0).

To do so, run...

```

pciload

```

...with no arguments, and the screen will display information about each unit.

### Main board PCIe FPGA

The main board PCIe FPGA is configured automatically at power-on via flash memory. This FPGA generally does not need to be reconfigured or updated unless...

- you are asked to do so by EDT during a support call or email exchange; or

- you install a new driver.

To verify the loading of the correct main board PCIe FPGA configuration file (pe81x4.bit or pe81x16.bit):

- 1. Navigate to the directory in which you installed the driver. The default location is \EDT\pcd in Windows.

- 2. At the prompt, enter...

```

pciload verify

```

...to compare the PCIe FPGA configuration file in the installation package with the one already loaded in flash memory. If multiple boards are installed, enter...

```

pciload -u unit# verify

```

...replacing unit# with the unit number.

If the dates and revision numbers match, there is no need to upgrade. If they differ, you can proceed through the steps below to upgrade the flash memory.

3. At the prompt, enter...

```

pciload update

```

4. Power-cycle the host computer (power off, then on – a simple reboot is not enough) to implement the new FPGA configuration file.

### Main board UI FPGA and mezzanine board 3P FPGA

The main board UI FPGA is configured automatically when you manually load the mezzanine board 3P FPGA. If necessary, you can set up the 3P directly by reading and writing the onboard registers; however, to do so, you must manually load the UI FPGA before loading the 3P FPGA.

To set up the board with either the automatic or the manual (direct) setup option...

1. For automatic setup of the UI FPGA and the mezzanine board 3P FPGA, skip to the next step.

For manual (direct) setup of the UI FPGA, run the bitload utility...

```

bitload -u unit# threep

```

...replacing unit# with the unit number.

2. Next, to set up the 3P FPGA, run the mezzload utility...

```

mezzload -u unit#

```

...replacing unit# with the unit number.

If you do not specify an FPGA configuration file, then mezzload will load the following file...

```

threep_stm64_sdh_sdh.bit

```

If you do wish to specify an FPGA configuration file, then enter...

mezzload -u unit# FPGAconfigurationfilename

...replacing unit# and FPGAconfigurationfilename with the appropriate information.

# Initializing the Clock Signals and Logic Circuits

This procedure initializes basic board operations, as well as communication between the main board's UI FPGA and the mezzanine board's 3P FPGA. Such communication is synchronized to the 100 MHz reference clock signal, which is initialized automatically upon main board startup but then must be distributed to the 3P FPGA. Until the 3P FPGA is synchronized to the reference clock signal, the main board cannot read or write any registers on the 3P mezzanine board (which reside in the range from 0x80 to 0xFF).

The EDTOCX member function board->BaseInit() determines the kind of board installed in your system, loads the main and mezzanine FPGA configuration files if needed, and performs the steps below. It uses an EDTOCXCfg structure to set bits 0 and 3 (SSWAP and BSWAP) in 0x0F Configuration as needed for your host, as well as to set other fields. For details on filling in the fields in this structure, consult the EDT API documentation (see Related Resources on page 11); for an example of its use, see the example application OCXSnap.cpp.

The routine board->BaseInit() typically is used to initialize clock signals and logic circuits.

To do so...

Load the appropriate firmware as described in Configuring the 3P: Initialization and Setup on page 16. The firmware will perform various actions, including initializing the main board PLL that generates the 100 MHz reference clock.

#### **NOTE**

If the firmware is loaded already and you do not wish to reload it, clear 0x00–7F [See threep.bit] and then clear the appropriate enable registers (0x83–84 for port 0, 0xA3–A4-for port 1, 0xC3–C4 for port 2) by writing all zeroes.

- 2. To initialize the logic circuits in the UI FPGA on the main board, set bit 3 (CMD\_EN) in 0x00–7F [See threep.bit].

- 3. To ensure that the FPGAs on the 3P mezzanine board have been synchronized, verify that bit 5 (SYS\_LOCK) of 0x84 Port 0 Enable is set.

- To ensure that the main board's UI FPGA has been synchronized, verify that bit 0 (LOCAL\_SYS\_LOCK) of 0x06

PLL Status is set.

- 5. At this point, insert a timeout in your application (the library routine <code>edt\_ocx\_base\_init</code> does so). The bits in steps 3 and 4 should be set within approximately 10 milliseconds of the bits in steps 2 and 3; if they are not, there is probably a fault in the board. In such a case, without a timeout your application will hang; inserting a timeout of approximately half a second should resolve the issue.

- 6. If the bits in steps 3 and 4 still are not set, stop initialization and contact EDT.

The main board is now set up correctly; basic initialization is complete and does not need to be done again until the host computer is power-cycled.

# **Initializing the Memory**

After the system PLL is synchronized, you'll need to initialize the memory blocks on your 3P.

To do so...

- 1. Clear bit 0 (PHY\_RST) in 0xE4–E6 DDR2 Bank Status and Control.

- 2. Include a timeout for the RAM to finish initialization and for the refresh to stabilize for example: edt\_msleep(10)

- 3. Wait for bits 5 and 6 (PLL\_LOCK and PHY\_INITDONE) in 0xE4–E6 DDR2 Bank Status and Control to be set.

The memory now is available for use. This operation, too, need not be repeated until you restart your application.

# Enabling and Verifying the Input Signals – Ports 1 and 2

Each port has two digital phase-locked loops (PLLs) — one for the LIU and one for the FPGA — which must be locked to the incoming data. If the data is interrupted or not present, these PLLs must be reset. The data paths can be initialized independently, so you can perform this procedure for one port or DMA channel even if another is acquiring data.

To do so, follow the steps below.

1. Prepare a channel to acquire data by using the library routines...

```

board->PortSetRate()

port->IoPortSetup()

```

2. Lock the PLLs by using the library routine...

```

board->LockFrontend()

```

Except where noted, board->LockFrontend() performs the procedure below.

- 1. Clear bits 0 (LIU\_EN), 1 (TPLL\_EN), and 4 (RPLL\_EN) in the desired register (0x84 Port 0 Enable).

- 2. To enable the LIU, set bit 0 (SLK\_EN) bit in the desired register (0x84 Port 0 Enable).

- Wait approximately 100 milliseconds.

- 4. Verify that the SFP transceiver module has detected an incoming signal by checking bit 7 (SIG\_DET) in the desired register (0xA2 Port 1 Status).

- 5. Loop until bit 7 (SIG\_DET) is set, showing application status as necessary.

- 6. To ensure that the LIU PLL is locked, verify that bit 4 (LOL) in the desired register (0xA2 Port 1 Status) is clear; if it is set, the LIU is not receiving a stable input signal in the range of the selected reference clock. In certain cases, the LOL bit can be clear even if the PLL is not locked. If the phase difference between the incoming data and the reference clock differs by more than 500 parts per million, the LOL state is not valid (for details on the SDH LIU, see Related Resources on page 11).

- 7. For incoming framed SONET / SDH signals, you may wish to verify that bit 5 (LOS) in the desired register (0xA2 Port 1 Status) is clear; if it is set, the LIU is not receiving a framed SONET / SDH signal. (Bit 5 can be clear only for framed SONET / SDH signals and is meaningless for other signals.) This step is not performed by board->Lock-Frontend().

- 8. To enable the PLLs in the FPGA that communicates with the LIU: Set bits 1 (TPLL\_EN) and 4 (RPLL\_EN) in the desired register (0x84 Port 0 Enable).

- 9. To verify that the receive clock PLL is locked to the receive clock of the LIU, verify that bits 6 and 7 (THREEP\_RX\_LOCKED and THREEP\_TX\_LOCKED) of the desired register (0x84 Port 0 Enable) are set. If they are clear, the board is not receiving an input signal, so you'll need to restart the data path initialization procedure from the beginning.

#### **NOTE** Your code can implement steps 1 through 9 as a loop.

- 10. If you are receiving a framed SONET/SDH signal, you can verify that it is properly framed and gather statistics about the quality of signal framing. Bit 7 (LOCKED) in 0xA8 Port 1 Receive Frame Status tells you if the signal is currently in frame. The library routine board->EnableFramingErrors enables the error counter registers, which track how many errors have occurred in signal framing and what types of errors they are. This routine sets bit 7 (EN COUNTERS) in 0x8B Port 0 Frame Statistics Count Control. The framing error registers are:

- 0xA8 Port 1 Receive Frame Status;

- 0x800105–07 Port 1 B1 Error Count;

- 0x800108–0B Port 1 B2 Error Count;

- 0x80010C–0E Port 1 M1 Error Count;

- 0x80010F–10 Port 1 Loss of Frame Count;

- 0x800111–12 Port 1 Frame Pattern Error Count.

3P Mezzanine Board Framing

The library routine board->EnableFramingErrors accesses these registers and returns the information by filling in the structure EdtoCXFrameErrors defined in edt\_ocx.h.

# **Initializing and Enabling the Data Paths**

To initialize and enable the data paths...

- 1. Configure DMA as required, using the library routine board->SetupDma().

- 2. Set up and enable each port / DMA channel using the C++ library routine board->ChannelStart().

- 3. Start DMA using the library routine edt\_start\_ring\_buffers.

- 4. Your application can now start transmitting or receiving data by setting the appropriate bits (0–3, CH\_ENABLE) in 0x10–11 DMA Channel Enable, or by calling the library function board->SetChannelEnable().

# Querying the SFP/+ Transceivers

Each SFP/+ transceiver has a two-wire serial interface that lets you query its state, including:

- The laser's transmit power, in decibels;

- The laser's receive power, in decibels; and

- The temperature of the SFP/+ in degrees Celsius.

For details, see the manufacturer's product information for the SFP/+ you are using (see Related Resources on page 11).

By default, each SFP/+ is enabled.

The application ReadXFPSFP will let you query and control each SFP/+ via the two-wire serial interface.

• To enable the SFP/+ via the two-wire serial interface, enter...

```

ReadXFPSFP -e 1

```

• To disable the SFP/+ via the two-wire serial interface, enter...

```

ReadXFPSFP -e 0

```

To turn on the laser after the SFP/+ is enabled, enter...

```

ReadXFPSFP -1 1

```

• To turn off the laser while keeping the SFP/+ enabled, enter...

```

ReadXFPSFP -1 0

```

## **Time Code**

The 3P uses the same timecode interface as the EDT Time Distribution board. For details, see registers 0xEB–ED Time Distribution and the Time Distribution user's guide (Related Resources on page 11).

# **Framing**

The 3P supports framing capability for OTN, OC / STM, and 10GbE, as described below.

3P Mezzanine Board Framing

### OTN and OC / STM

For OTN and OC / STM, framing headers are included in the data transferred during DMA. If framing is enabled, the board searches and locks onto incoming SONET / SDH frames after detecting the presence of A1 and A2 header patterns at 125-millisecond intervals. The algorithm sequence is...

- 1. Search. The board searches for A1 and A2 header patterns until it sees a match; then it goes to Check.

- 2. Check. The board checks for three consecutive SONET / SDH frames at 125-microsecond intervals with the A1 and A2 header patterns in the proper position, before declaring Lock.

- 3. Lock. Once locked, incoming SONET / SDH frames are collected and forwarded to the host. The board continues to check for the A1 and A2 header patterns, and remains in this state until the A1 and A2 header patterns are lost. When the patterns are lost, it enters the Flywheel state.

- Flywheel. If the A1 and A2 header patterns are not seen for three consecutive frames, the board returns to Search;

if it finds them, it returns to Lock. SONET / SDH frames are collected and forwarded to the host in this state as well.

### **10 GbE**

For 10 GbE, framing information is provided in such registers as...

- 0x85 Port 0 Receive Framing Control;

- 0x86 Port 0 Receive Filter Control;

- 0x8E Port 0 PCS Control.

For details, contact EDT (tech@edt.com).

3P Mezzanine Board Basic Self-Testing

# **Basic Self-Testing**

The loopback test determines the board configuration, loads the appropriate FPGA configuration file, generates test data, and tests the board and its components with no external device connected. For included test files, see Basic Testing on page 14 (under Sample Applications).

#### **NOTE**

The loopback test overwrites the FPGA configuration file in the UI FPGA. After completing the test, you must reconfigure the board before using it again.

To perform the loopback test:

- 1. Keep the board in the host computer with the mezzanine board (if any) attached, but disconnect any external device and its cabling.

- 2. In a command window, enter...

```

sslooptest -u unit number

```

The outcome varies depending on your main-mezzanine board pair. Errors are directed to the file sslooptest.err in the current directory; if no such file exists, the test completed without errors.

Loopback test output for a functional board contains such lines as:

- The value after Total errs shows the error count so far.

- The value after bufs shows the number of buffers in use.

- The characters after Channel errs correspond to DMA channels 0-15 (in that order). For each DMA channel, Y means a data error, N means no data error, and X means that channel is not in use.

- The characters after Channel... bufs also correspond to DMA channels 0-15. For each DMA channel, Y means the buffer is in use, N means no DMA is occurring, and X means that channel is not in use.

- 3. After the test is done, reconfigure the board with initped (or your own application) to disable loopback.

- 4. Reconnect the board to the external device.

3P Mezzanine Board Board Architecture

# **Board Architecture**

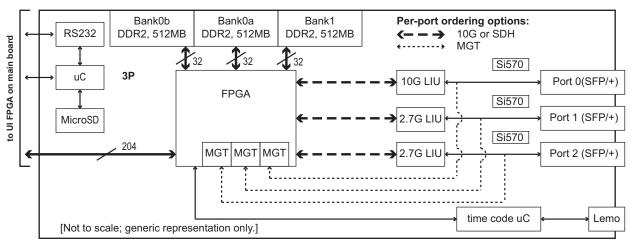

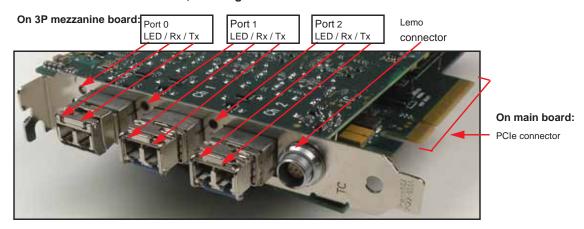

The 3P mezzanine board works with an EDT main board. Figure 2 shows various features on the 3P alone, while Figure 3 shows the 3P with a main board and indicates the location of the connectors and LEDs.

Figure 2. Block diagram – 3P mezzanine board

NOTES: Banks 0b and 0a can be combined as a 64-bit-wide 1GB memory bank.

Si570 oscillators are programmable via I2C and provide reference clocks directly to LIUs and MGTs.

Figure 3. 3P mezzanine with main board, showing connectors and LED status indicators

The 3P mezzanine board (on top) shows the SFP/+ transceivers with their port connections, and the Lemo connector for timecode input. The main board (on the bottom) shows the location of the PCIe connector.

**NOTE**

The 3P ports are labeled on the front panel as follows: "Ch 0" (port 0) is the SFP/+ furthest from the PCIe connector; "Ch 2" (port 2) is the SFP/+ nearest the PCIe connector.

Each port has one bicolor LED (controlled by the 3P FPGA) to indicate the status of that port in three areas:

- Is the FPGA receive clock locked?

- Is a signal being received?

- Is the signal being framed?

3P Mezzanine Board Board Architecture

If a port is working properly in all three areas, its LED will be green. If a port has problems with receiving and framing a signal, its LED will be red. If a port has a combination of red and green conditions, the two colors will combine to make a third color, which is orange.

If you are using an EDT FPGA configuration (.bit) file, during board initialization each port's LED initially will blink red or orange, and then will change to steady red, orange, or green.

Table 3 summarizes these LED behaviors.

Table 3. LED behaviors generated by EDT FPGA configuration (.bit) files

| LED behavior    | Clock locked? | Signal received? | Signal framed? |

|-----------------|---------------|------------------|----------------|

| Blinking red    | No            | No               | No             |

| Blinking orange | No            | Yes              | No             |

| Steady red      | Yes           | No               | No             |

| Steady orange   | Yes           | Yes              | No             |

| Steady green    | Yes           | Yes              | Yes            |

# APPENDIX A: Main Board UI FPGA Configuration File

# **Overview**

This appendix documents the registers for the following main board UI FPGA configuration files, as found in your EDT installation package.

threep.bit

For the main board UI FPGA (on the PCle8 LX/FX/SX main board).

# threep.bit

# 0x00-0x7F Main Board

### 0x00 Command

|     |        | Access / Notes  | 8-bit read-write / PCD_CMD                                                                                                                                                                |

|-----|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Access | Name            | Description                                                                                                                                                                               |

| 7–4 | _      | PCD_STAT_INT_EN | Enables interrupts as defined in registers 0x03 Interrupt Status and 0x04 Interrupt Enable.                                                                                               |

| 3   | RW     | CMD_EN          | Set this bit and enable the required DMA channels in 0x10–11 DMA Channel Enable for DMA. When clear, resets all DMA channels, flushes all FIFOs, and clears all under- and overflow bits. |

| 2-0 | -      | [no name]       | Reserved.                                                                                                                                                                                 |

# 0x03 Interrupt Status

|     |        | Access / Notes | 8-bit read-only / PCD_STAT                                                                                                                                                                                   |

|-----|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |                | This register is connected to 1Hz test interrupt as an example of interrupts generated by the UI FPGA on the main board.                                                                                     |

| Bit | Access | Name           | Description                                                                                                                                                                                                  |

| 7–4 | R only | PCD_STAT_INT   | Interrupt bits for the status bits. If the corresponding bit is asserted in $0x00$ Command, then the corresponding bit of these four can be asserted to cause a PCI bus interrupt.                           |

|     |        |                | The PCI bus interrupt then is caused when the corresponding PCD_STAT signal [bits 3–0] is asserted. To reset the interrupt, disable and re-enable the appropriate PCD_STAT_INT_EN bit [7–4] in 0x00 Command. |

| 3–0 | R only | PCD_STAT       | The state of user-definable STAT input signals as last sampled.                                                                                                                                              |

# 0x04 Interrupt Enable

|     |        | Access / Notes       | 8-bit read-write / PCD_STAT_POLARITY                                                                                                                                                                                                                              |

|-----|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |                      | This register is connected to 1Hz test interrupt as an example of interrupts generated by the UI FPGA on the main board.                                                                                                                                          |

| Bit | Access | Name                 | Description                                                                                                                                                                                                                                                       |

| 7–5 | _      | [no name]            | Reserved.                                                                                                                                                                                                                                                         |

| 4   | RW     | PCD_STAT_INT_<br>ENA | Provides global enable or disable for all interrupt bits [7–4] in 0x03 Interrupt Status above, allowing the driver to disable and re-enable them in one operation without altering their states. A value of 1 enables the interrupts; a value of 0 disables them. |

| 3–0 | -      | [no name]            | Reserved.                                                                                                                                                                                                                                                         |

### 0x05 FPGA Configuration File Organization

Access / Notes 8-bit read-only / PCD\_ORG

Bit Access Name Description

7-0 R only [no name] Specifies the organization that created the FPGA configuration file currently loaded in the

UI FPGA on the main board. An EDT FPGA configuration file returns the value 0xFF.

### 0x06 PLL Status

Access / Notes 8-bit read-only / [no name]

| Bit | Access | Name           | Description                                                                                       |

|-----|--------|----------------|---------------------------------------------------------------------------------------------------|

| 7–1 | _      | [no name]      | Reserved.                                                                                         |

| 1   | R only | [no name]      | If set, the 100 MHz clock used for data transfers from the mezzanine to the main board is locked. |

| 0   | R only | LOCAL_SYS_LOCK | If set, the 100 MHz reference clock is locked.                                                    |

### **0x0F** Configuration

Access / Notes 8-bit read-write / PCD\_CONFIG

This register and register 0x16 both can affect how data is ordered.

| Bit | Acces | s Name    | Description                                                                                                                                                                                      |

|-----|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4 | _     | [no name] | Reserved.                                                                                                                                                                                        |

| 3   | RW    | SSWAP     | Short swap bit; swaps the two 16-bit short words in one 32-bit data word, so that <i>short 1</i> is transferred before <i>short 0</i> . Does not change the order of the bits within each short. |