## **User's Guide**

## PCle8g3 S5 Family

# PCIe Gen3 x8 boards with Stratix V FPGA and 10G / 40G ports

Date: 2017 January 04

Rev.: 0001

| EDT <sup>TM</sup> and Engineering Design Team <sup>TM</sup> are trademarks of Engineering Design Team, Inc. All other trademarks, service marks, |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| and copyrights are the property of their respective owners <sup>†</sup> .                                                                        |

| © 1997-2015 Engineering Design Team, Inc. All rights reserved.                                                                                   |

International Distributors

Sky Blue Microsystems GmbH Geisenhausenerstr. 18 81379 Munich, Germany +49 89 780 2970, info@skyblue.de www.skyblue.de

In Great Britain:

Zerif Technologies Ltd.

Winnington House, 2 Woodberry Grove

Finchley, London N12 0DR

+44 115 855 7883, info@zerif.co.uk

www.zerif.co.uk

EDT, Inc. 2

#### **Terms of Use Agreement**

**Definitions.** This agreement, between Engineering Design Team, Inc. ("Seller") and the user or distributor ("Buyer"), covers the use and distribution of the following items provided by Seller: a) the binary and all provided source code for any and all device drivers, software libraries, utilities, and example applications (collectively, "Software"); b) the binary and all provided source code for any and all configurable or programmable devices (collectively, "Firmware"); and c) the computer boards and all other physical components (collectively, "Hardware"). Software, Firmware, and Hardware are collectively referred to as "Products." This agreement also covers Seller's published Limited Warranty ("Warranty") and all other published manuals and product information in physical, electronic, or any other form ("Documentation").

License. Seller grants Buyer the right to use or distribute Seller's Software and Firmware Products solely to enable Seller's Hardware Products. Seller's Software and Firmware must be used on the same computer as Seller's Hardware. Seller's Products and Documentation are furnished under, and may be used only in accordance with, the terms of this agreement. By using or distributing Seller's Products and Documentation, Buyer agrees to the terms of this agreement, as well as any additional agreements (such as a nondisclosure agreement) between Buyer and Seller.

**Export Restrictions.** Buyer will not permit Seller's Software, Firmware, or Hardware to be sent to, or used in, any other country except in compliance with applicable U.S. laws and regulations. For clarification or advice on such laws and regulations, Buyer should contact: **U.S. Department of State, Washington, D.C., U.S.A.**

**Limitation of Rights.** Seller grants Buyer a royalty-free right to modify, reproduce, and distribute executable files using the Seller's Software and Firmware, provided that: a) the source code and executable files will be used only with Seller's Hardware; b) Buyer agrees to indemnify, hold harmless, and defend Seller from and against any claims or lawsuits, including attorneys' fees, that arise or result from the use or distribution of Buyer's products containing Seller's Products. Seller's Hardware may not be copied or recreated in any form or by any means without Seller's express written consent.

**No Liability for Consequential Damages.** In no event will Seller, its directors, officers, employees, or agents be liable to Buyer for any consequential, incidental, or indirect damages (including damages for business interruptions, loss of business profits or information, and the like) arising out of the use or inability to use the Products, even if Seller has been advised of the possibility of such damages. Because some jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to Buyer. Seller's liability to Buyer for actual damages for any cause whatsoever, and regardless of the form of the action (whether in contract, product liability, tort including negligence, or otherwise) will be limited to fifty U.S. dollars (\$50.00).

Limited Hardware Warranty. Seller warrants that the Hardware it manufactures and sells shall be free of defects in materials and workmanship for a period of 12 months from date of shipment to initial Buyer. This warranty does not apply to any product that is misused, abused, repaired, or otherwise modified by Buyer or others. Seller's sole obligation for breach of this warranty shall be to repair or replace (F.O.B. Seller's plant, Beaverton, Oregon, USA) any goods that are found to be non-conforming or defective as specified by Buyer within 30 days of discovery of any defect. Buyer shall bear all installation and transportation expenses, and all other incidental expenses and damages.

Limitation of Liability. In no event shall Seller be liable for any type of special consequential, incidental, or penal damages, whether such damages arise from, or are a result of, breach of contract, warranty, tort (including negligence), strict liability, or otherwise. All references to damages herein shall include, but not be limited to: loss of profit or revenue; loss of use of the goods or associated equipment; costs of substitute goods, equipment, or facilities; downtime costs; or claims for damages. Seller shall not be liable for any loss, claim, expense, or damage caused by, contributed to, or arising out of the acts or omissions of Buyer, whether negligent or otherwise.

**No Other Warranties.** Seller makes no other warranties, express or implied, including without limitation the implied warranties of merchantability and fitness for a particular purpose, regarding Seller's Products or Documentation. Seller does not warrant, guarantee, or make any representations regarding the use or the results of the use of the Products or Documentation or their correctness, accuracy, reliability, currentness, or otherwise. All risk related to the results and performance of the Products and Documentation is assumed by Buyer. The exclusion of implied warranties is not permitted by some jurisdictions. The above exclusion may not apply to Buyer.

**Disclaimer.** Seller's Products and Documentation, including this document, are subject to change without notice. Documentation does not represent a commitment from Seller.

EDT, Inc.

## **Contents**

| Contents                                             | 4  |

|------------------------------------------------------|----|

| Overview                                             | 7  |

| Related Resources                                    | 8  |

| Care and Cautions                                    | 8  |

| Installation and the EDT Installation Package        | 9  |

| The PCD Device Driver                                | 9  |

| Firmware: FPGA Configuration (.bit) Files            | 9  |

| Applications and Utilities                           | 10 |

| Building or Rebuilding an Application                | 11 |

| Configuring the S5                                   | 11 |

| Unit Number                                          | 11 |

| FPGA                                                 | 12 |

| Initialization and Setup                             | 13 |

| Initializing Memory and Data Path                    | 13 |

| Initializing Ports                                   | 13 |

| Querying the Transceivers                            | 14 |

| Time Code                                            | 14 |

| Framing                                              | 14 |

| Hardware                                             | 15 |

| Block Diagrams                                       | 15 |

| Ports and LED Status Indicators                      | 16 |

| Registers, UI                                        | 18 |

| 0x00-0x7F Indirect                                   | 18 |

| 0x00 Command                                         | 18 |

| 0x03 Interrupt Status                                | 18 |

| 0x04 Interrupt Enable                                | 18 |

| 0x0D Exended Configuration                           | 19 |

| 0x0F Configuration                                   | 19 |

| 0x10-11 DMA Channel Enable                           | 20 |

| 0x16–17 Least Significant Bit First                  | 20 |

| 0x18–19 Underflow                                    | 20 |

| 0x1A-1B Overflow                                     | 20 |

| 0x60-62 Extended Indirect Register Address           |    |

| 0x63 Extended Indirect Register Data                 | 21 |

| 0x64 Serial Master Interface Status                  | 21 |

| 0x65 Serial Master Interface Read [7-0]              | 22 |

| 0x66 Serial Master Interface Register Address [7–0]  |    |

| 0x67 Serial Master Interface Write [7–0]             | 22 |

| 0x68 Serial Master Interface Read [15–8]             | 22 |

| 0x69 Serial Master Interface Register Address [15–8] | 22 |

| 0x6A Serial Master Interface Write [15–8]            | 23 |

| 0x6B Reference Clock Control                         | 23 |

| 0x6C Sync Trigger Control and Status                 | 23 |

| 0x6D SPI Data                                        | 23 |

| 0x6E SPI Status and Control                          | 24 |

| 0x6F SPI Strobe                                      |    |

| 0x7C-7D FPGA Configuration File Design ID            | 24 |

| 0x7E FPGA Configuration File Version String          |    |

| 0x7F Board ID [Reserved]                             |    |

| Registers, UI                                        | 26 |

| 0x000000-0x7FFFFF BAR1 Memory-Mapped                                             |    |

|----------------------------------------------------------------------------------|----|

| 0x000010 Data Path and Memory Control                                            | 26 |

| 0x000014 Memory Status                                                           |    |

| 0x000018 W PRBS [Reserved]                                                       | 27 |

| 0x00001C W PRBS 2 [Reserved]                                                     | 27 |

| 0x000024 Memory Loop Size                                                        | 27 |

| 0x000028 Memory Information                                                      | 27 |

| Registers, Port: Ports 0–3 (SFPs)                                                | 28 |

| 0x80–0x9F Indirect                                                               |    |

| 0x80, 88, 90, 98 SFP Configuration and Status                                    |    |

| 0x82, 8A, 92, 9A Port Status                                                     |    |

| 0x87, 8F, 97, 9F Port Information                                                |    |

| Registers, Port: Ports 0–3 (SFPs)                                                |    |

| 0x800000–0x837FFF BAR1 Memory-Mapped                                             |    |

| 0x800000, 810000, 820000, 830000 Receive Framer Status and Control               |    |

| 0x800004, 810004, 820004, 830004 Receive Filter                                  |    |

| 0x800008, 810008, 820008, 830008 Transmit Framer Control [Reserved]              |    |

| 0x80000C, 81000C, 82000C, 83000C Line Rate / Protocol Control                    |    |

| 0x800010, 810010, 820010, 830010 Synchronization Control                         |    |

| 0x800014, 810014, 820014, 830014 Frame Statistics Count Control                  |    |

| 0x800018, 810018, 820018, 830018 Transmit National Byte                          |    |

| 0x80001C, 81001C, 82001C, 83001C Transmit Test Pattern                           |    |

| 0x800020, 810020, 820020, 830020 Last B1 Error                                   |    |

| 0x800024, 810024, 820024, 830024 B1 Error Count                                  |    |

| 0x800024, 810024, 820024, 830024 BT Effor Count                                  |    |

| 0x80002C, 81002C, 82002C, 83002C M1 Error Count                                  |    |

|                                                                                  |    |

| 0x800030, 810088, 820088, 830088 Loss of Frame Count                             |    |

|                                                                                  |    |

| 0x80003C, 81003C, 82003C, 83003C Demux Bitmask                                   |    |

| 0x800040, 810040, 820040, 830040 Demux Bitmask Readback                          |    |

| 0x800060, 810060, 820060, 830060 Detailed Port Status                            |    |

| 0x800064, 810064, 820064, 830064 Transceiver Reconfiguration Address and Control |    |

| 0x800068, 810068, 820068, 830068 Transceiver Reconfiguration Write Data          |    |

| 0x80006C, 81006C, 82006C, 83006C Transceiver Reconfiguration Read Data           |    |

| 0x800074, 810074, 820074, 830074 Frequency Counter Enable                        |    |

| 0x800078, 810078, 820078, 830078 Receive Frequency Counter                       |    |

| 0x80007C, 81007C, 82007C, 83007C Transmit Frequency Counter                      |    |

| 0x800080, 810080, 820080, 830080 PRBS Mode                                       |    |

| 0x800084, 810084, 820084, 830084 PRBS Control 0                                  |    |

| 0x800088, 810088, 820088, 830088 PRBS Control 1                                  |    |

| 0x80008C, 81008C, 82008C, 83008C PRBS Control 2 [Reserved]                       |    |

| 0x800090, 810090, 820090, 830090 PRBS Control 3 [Reserved]                       |    |

| 0x800094, 810094, 820094, 830094 PRBS Control 4 [Reserved]                       |    |

| Registers, Port: Port 4 (QSFP)                                                   |    |

| 0xA0-0xA7 Indirect                                                               |    |

| 0xA0 QSFP Configuration and Status                                               |    |

| 0xA1 Port Enable                                                                 |    |

| 0xA2 Port Status                                                                 |    |

| 0xA3 QSFP Status 2 [Reserved]                                                    |    |

| 0xA7 Port Information                                                            |    |

| Registers, Port: Port 4 (QSFP/+)                                                 | 43 |

| 0x840010-0x840098 BAR1 Memory-Mapped                                             |    |

| 0x840010 Synchronization Control                                                 |    |

| 0x840014 Frame Count Control [Reserved]                                          | 43 |

|                                                                                  |    |

EDT, Inc.

|            | 0x840060 Detailed Port Status                            | 43 |

|------------|----------------------------------------------------------|----|

|            | 0x840064 Transceiver Reconfiguration Address and Control | 44 |

|            | 0x840068 Transceiver Reconfiguration Address and Control | 44 |

|            | 0x84006C Transceiver Reconfiguration Address and Control | 44 |

|            | 0x840074 Frequency Counter Enable                        | 44 |

|            | 0x840078 Receive Frequency Counter                       | 44 |

|            | 0x84007C Transmit Frequency Counter                      |    |

|            | 0x840080 PRBS Mode                                       | 45 |

|            | 0x840084 PRBS Control 0                                  | 45 |

|            | 0x840088 PRBS Control 1                                  |    |

|            | 0x84008C PRBS Control 2 [Reserved]                       | 46 |

|            | 0x840090 PRBS Control 3 [Reserved]                       | 46 |

|            | 0x840094 PRBS Control 4 [Reserved]                       |    |

| Revision I | _og                                                      | 48 |

|            |                                                          |    |

PCIe8g3 S5 Family Overview

## PCle8g3 S5 Family

## **Overview**

The PCIe8g3 S5 ("S5") family is a group of multiport, multirate interfaces. Currently this family includes two versions...

- The S5 10G so named because it can support up to four 10G transceivers.

- The S5 40G so named because it can support one 40G transceiver, plus two 10G transceivers.

Each version includes...

- One Altera Stratix V GX FPGA, with multiple options available;

- One eight-lane PCIe Gen 3 DMA interface;

- Two independent 4 GB banks of DDR3 DRAM, for a total of 8 GB;

- Four programmable oscillators (one per port);

- Support for a jitter-attenuated recovery clock; and

- A variety of transceiver options.

Table 1 shows the transceiver options (by port) for each version.

Table 1. S5 10G and 40G - options by port

| S5  | Port | DMA channel                       | Transceiver      | Wavelength(s)      | Signal(s)*                        |

|-----|------|-----------------------------------|------------------|--------------------|-----------------------------------|

| 10G | 0    | 0                                 | SFP              | 1550, 1310, 850 nm | 1GbE; OC3/12/48 (STM1/4/16); OTU1 |

|     |      |                                   | SFP+             | 1550, 1310 nm      | 10GbE; OC 192 (STM64); OTU2/2e/2f |

|     |      |                                   | SFP+             | 850 nm             | 10GbE only                        |

|     | 1    | 1                                 | [same as port 0] |                    |                                   |

|     | 2    | 2                                 | [same as port 0] |                    |                                   |

|     | 3    | 3                                 | [same as port 0] |                    |                                   |

| 40G | 0    | 0                                 | SFP              | 1550, 1310, 850 nm | 1GbE; OC3/12/48 (STM1/4/16); OTU1 |

|     |      |                                   | SFP+             | 1550, 1310 nm      | 10GbE; OC 192 (STM64); OTU2/2e/2f |

|     |      |                                   | SFP+             | 850 nm             | 10GbE only                        |

|     | 1    | 1                                 | [same as port 0] |                    |                                   |

|     | 4    | $0 \text{ (when sel\_port } = 4)$ | QSFP+            | 850 nm             | 40GbE                             |

$<sup>^{\</sup>star}$  SONET (OC3/12/48) and SDH (STM1/4/16) signal names are used interchangeably.

For signal standards, see Related Resources on page 8.

For port locations and other board features, see Hardware on page 15.

PCIe8g3 S5 Family Overview

### **Related Resources**

To find product-specific information that is related to a particular EDT product, go to www.edt.com and open the relevant product page. There you'll see links to that product's datasheet (specifications), user's guide, and other resources.

The resources may be helpful or necessary for your applications.

#### **EDT Resources**

Application programming interface (API) www.edt.com/api/

Installation packages (Windows, Linux, Mac) www.edt.com/software

PCle8g3 S5-10G datasheet (specifications)

www.edt.com/pcie8g3s5-10g.html

PCle8g3 S5-40G datasheet (specifications)

www.edt.com/pcie8g3s5-40g.html

Time Distribution datasheet (specifications) / user's guide www.edt.com/timedist.html

Static Discharge Kit instructions

www.edt.com/static

#### **Third-Party Resources**

Standards / Specifications

PCI Express (PCIe)

www.pcisig.com

• IRIG-B irigb.com

International Telecommunications Union (ITU) / Optical Transport Network (OTN) / www.itu.int

G.709/Y.133103/2003

• Ethernet framing (IEEE 802-3) www.ieee802.org/3/

Parts

FPGA: Altera Stratix V GX

www.altera.com

### **Care and Cautions**

Although EDT products are built to specifications which allow them to withstand a variety of extreme conditions, they are still high-performance components which require proper care for best results. To protect them and your equipment, follow all recommended instructions for care and cautions, including those in the EDT-provided static discharge kit.

For links to datasheet specifications and EDT static discharge kit instructions, see Related Resources.

## Installation and the EDT Installation Package

To physically install your S5 board, follow the steps below while referring to Hardware on page 15.

- 1. Since each transceiver can be unique, notate the position of each transceiver on your S5 board so you can return each one to its proper place later.

- 2. Remove the transceivers to enable the board to be inserted into the host system.

- 3. Insert the board into the host system.

- 4. Working through the back panel on the host system, return each transceiver to its original position on the S5 board.

#### NOTE

We recommend powering off the board before replacing any transceiver, despite manufacturers' claims that transceivers are hot-swappable.

Now you're ready to review the resources included in the EDT installation package. In addition to the files listed below, custom FPGA configuration files can be requested.

#### The PCD Device Driver

Your EDT installation package contains the PCD device driver – the software that runs on the host computer and allows the host operating system to communicate with the S5. The driver is loaded into the kernel at installation and thereafter runs as a kernel module. The driver name and subdirectory is specific to each supported operating system, and the installation script automatically installs the appropriate device driver in the appropriate way for your operating system.

## Firmware: FPGA Configuration (.bit) Files

Your EDT installation package includes firmware in the form of FPGA configuration (.bit) files. The correct .bit file for your specific S5 board and FPGA is located and loaded as below.

|                           |                 | For the .bit file named | Which is loaded                  |

|---------------------------|-----------------|-------------------------|----------------------------------|

| The FPGA on your S5 board | flash/FPGApart# | pe8s5_4p.bit            | Automatically, from flash memory |

If you need to reload the firmware due to corruption or an update, see Configuring the S5 on page 11.

## **Applications and Utilities**

In addition to the above resources, the EDT installation package includes application and utility files that you can use to initialize and configure the board, access the registers, and perform basic testing. In many cases, C or C++ source is provided so that you can use the files as starting points to write your own applications. The most commonly useful files are described below.

#### **NOTE**

For a link to the latest installation packages, see Related Resources on page 8. For new installations, use the latest package. For existing applications, to avoid version problems, upgrade only if you have a specific reason to do so.

These S5-specific files are included in the libs5 or libocx directory of your EDT installation package...

fourp Utility to set up and initialize the S5.

fourp.cpp Source file for the fourp utility.

EdtS5Xcvr.cpp C++ object describing EDT Stratix 5 FPGA's transceiver.

EdtS5Xcvr.h Include file for the above C++ object.

EdtS5Mem.cpp C++ object describing EDT Stratix 5 DDR3 memory and data flow.

EdtS5Mem.h Include file for the above C++ object.

EdtS5.cpp C++ object describing any EDT board based on Stratix 5 FPGA.

Edt4P.cpp Include file for the above C++ object.

Edt4P.cpp C++ object describing EDT S5 board.

Edt4P.h Include file for the above C++ object.

edt\_fourp.h Include file.

In the future, the S5 is scheduled to be supported by such additional applications as...

OCXSnap Example application that captures data from the S5 board and transfers it to disk

for testing or verification.

OCXSnap.cpp C source for OCXSnap.

OCXPlay Example application that outputs the data captured by OCXSnap from the disk for

testing or verification.

OCXPlay.cpp C source for OCXPlay.

ReadXFPSFP Example application that queries the state of the transceiver modules. For details,

see Initializing Ports on page 13.

ReadXFPSFP.cpp C source for ReadXFPSFP.

EdtSFP.cpp C library routines used by ReadXFPSFP or available for you to use in your own

application.

EdtSFPPlus.cpp C library routines used by ReadXFPSFP or available for you to use in your own

application.

## **Sample Applications**

wr16

rd16 For DMA channels – performs simple multichannel ring buffer input.

simple\_read Performs DMA input without using ring buffers. Data is therefore subject to

interruptions, depending on system performance.

For DMA channels – performs simple multichannel ring buffer output.

simple\_write Performs DMA output without using ring buffers. Data is therefore subject to

interruptions, depending on system performance.

PCIe8g3 S5 Family Configuring the S5

simple\_getdata Serves as an example of a variety of DMA-related operations, including reading the

data from the connector interface and writing it to a file, as well as measuring input

rate.

simple\_putdata Serves as an example of a variety of DMA-related operations, including reading

data from a file and writing it out to the connector interface.

test\_timeout In typical operation, timeouts cancel DMA transfers. This application exemplifies

giving notification of timeouts, without canceling DMA.

#### **Utilities**

gstemp Utility for monitoring the temperature of the S5.

pdb Enables interactive reading and writing of the UI FPGA registers.

set\_si570 Programs the S5 reference clock(s) to specific frequencies used by the S5 FPGA

for input and output.

timing\_test Tests the timecode input.

## **Building or Rebuilding an Application**

In your EDT installation package, executable and PCD source files are in the top-level directory. Therefore, if you need to build or rebuild an application, run make in that directory.

Windows users must install a C compiler; we recommend the Microsoft Visual C compiler for Windows. Linux users can use the <code>gcc</code> compiler typically included with the Linux installation. If you use Windows and you wish to use <code>gcc</code>, contact tech@edt.com.

After you build or rebuild an application, use the --help command line option for a list of usage options and descriptions.

## Configuring the S5

The S5 has one FPGA, called the PCIe FPGA. This section explains how to...

- 1. Find the unit number (by default, 0) assigned to your S5 board by your system.

- 2. Configure the FPGA with the appropriate FPGA configuration file.

- 3. Configure the physical ports and the DMA channels.

To implement these steps and conduct loopback testing (see Basic Testing [main section - was between Framing and Hardware - no looptest now, but will be later] on page 49), use this section.

To begin data acquisition, further initialization is required (see Initialization and Setup on page 13).

## **Unit Number**

To see which EDT unit(s) are in your host system and to find their unit numbers, run...

pciload

...with no arguments, and the screen will display information about each one.

PCIe8g3 S5 Family Configuring the S5

#### **FPGA**

At power-on, the firmware (FPGA configuration or .bit file) is installed automatically via nonvolatile flash memory. Typically you do not need to reconfigure or update the firmware unless...

- you are asked to do so by EDT during a support call or email exchange;

- · you install a new driver; or

- the firmware becomes corrupted.

To verify the loading of the correct FPGA configuration file for your S5 board...

- 1. Navigate to the directory in which you installed the driver. The default locations are...

- For Windows, \EDT\pcd

- For Linux or Mac, /opt/EDTpcd

- 2. At the prompt, enter...

```

pciload verify

```

...to compare the FPGA configuration file in the installation package with the one already loaded in flash memory. If multiple boards are installed, enter the unit number after the -u option...

```

pciload -u unit number verify

```

If the dates and revision numbers match, there is no need to upgrade. If they differ, you can proceed through the steps below to upgrade the flash memory.

3. At the prompt, enter...

```

pciload update

```

4. Shut down the operating system; turn the host computer off, and then on again. The board reloads firmware from flash memory only during powerup. Thus, after running pciload, the new FPGA configuration file is not in the FPGA until the system has been power-cycled; simply rebooting is not adequate.

PCIe8g3 S5 Family Initialization and Setup

## **Initialization and Setup**

PCle8g3 S5 boards can be initialized and set up with the fourp utility. The recommended sequence is:

- 1. Initialize the DDR3 memory and set up the data path.

- 2. Initialize the ports as needed.

NOTE Some setup (such as of the memory and data path) affects all channels, so implement setup with caution.

## **Initializing Memory and Data Path**

To prepare for DMA, the data path must be initialized. Doing so includes setting the data path direction, determining whether data will be directed to DMA, and verifying that the DDR3 memory PHY has been initialized.

In the default FPGA configuration file provided with your S5 board, the two DDR3 memory banks are divided into two logical memory banks. In register 0x000010 Data Path and Memory Control, when port 0, 1, 2, or 3 is set, each port thus set is assigned a logical memory bank; when port 4 is set, then the four logical memory banks are combined into a single logical bank. In the same register, the latter result can be achieved with the fourp utility by entering...

```

fourp -rm -p 0 -D -rx

```

...where the flags have the following effects...

- The -rm flag resets the DDR3 PHY.

- The -p 0 flag sets the memory for ports 0, 1, 2, and 3.

- The -D flag sets the data path for DMA.

- The -rx flag sets the data path for receiving data.

**NOTE**

The -D flag always should be used with either the -rx or the -tx flag (-rx and -tx are mutually exclusive) and will affect all ports.

## **Initializing Ports**

Each port can be set up and used independently by using the fourp utility and adding the flags...

```

-p x // to determine which port is configured;

```

-R  $\,x\,$  // to determine which rate is set.

For example, you could enter these three commands, in any sequence...

```

fourp -p 0 -R stm64

fourp -p 1 -R otu2f

fourp -p 2 -R stm1

```

...in order to set port 0 to STM64, port 1 to OTU2f, and port 2 to STM1.

**NOTE**

When you specify a rate, the <code>fourp</code> utility does not verify whether a port's transceiver can support that rate. Therefore, you must be aware of which transceiver is in each port (the board can read this information for you) and what each transceiver's capabilities are.

Using the fourp utility in this way will set the respective port's reference clock and reconfigure the FPGA's SERDES appropriately; however, it will not set up the relevant port's framing register (0x800000, 810000, 820000, 830000 Receive Framer Status and Control) or demux bitmap register (0x80003C, 81003C, 82003C, 83003C Demux Bitmask), nor will it enable the relevant channel for DMA in registers 0x00 Command and 0x10–11 DMA Channel Enable.

PCIe8g3 S5 Family Framing

## **Querying the Transceivers**

To query the transceiver on a specified port, you can use fourp -p x with these flags...

```

-w // to query the received optical power

```

${\scriptscriptstyle -C}$  // to query the temperature

For example, you could enter such commands as...

```

fourp -p 0 -C // to query port 0 for received optical power fourp -p 1 -w // to query port 1 for temperature

```

...without disrupting the other ports or the DMA.

For details, see the manufacturer's website for the transceivers you are using (see Related Resources on page 8).

#### **Time Code**

The S5 uses the same timecode interface as the EDT Time Distribution board. For details, see these registers...

- Register 0x6D SPI Data

- Register 0x6E SPI Status and Control

- Register 0x6F SPI Strobe

...and consult the Time Distribution user's guide (Related Resources on page 8).

## **Framing**

The S5 default firmware (FPGA configuration file) supports framing capabilities as described below.

For 10GbE and 40GbE, currently only clear-bit data is supported.

For OTN and OC / STM, framing headers are included in the data transferred during DMA. If framing is enabled, the board searches and locks onto incoming SONET / SDH frames after detecting the presence of A1 and A2 header patterns at 125 ms intervals. The algorithm sequence is:

- 1. Search. The board searches for A1 and A2 header patterns until it sees a match; then it goes to Check.

- 2. Check. The board checks for three consecutive SONET / SDH frames at 125-microsecond intervals with the A1 and A2 header patterns in the proper position, before declaring Lock.

- 3. Lock. Once locked, incoming SONET / SDH frames are collected and forwarded to the host. The board continues to check for the A1 and A2 header patterns, and remains in this state until the A1 and A2 header patterns are lost. When the patterns are lost, it enters the Flywheel state.

- 4. Flywheel. If the A1 and A2 header patterns are not seen for three consecutive frames, the board returns to Search; if it finds them, it returns to Lock. SONET / SDH frames are collected and forwarded to the host in this state as well.

PCIe8g3 S5 Family Hardware

## **Hardware**

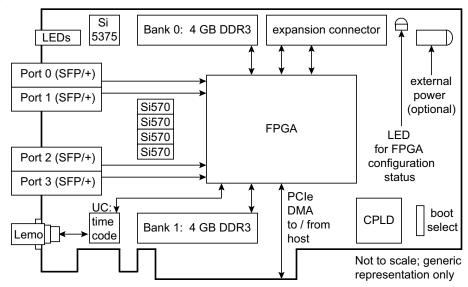

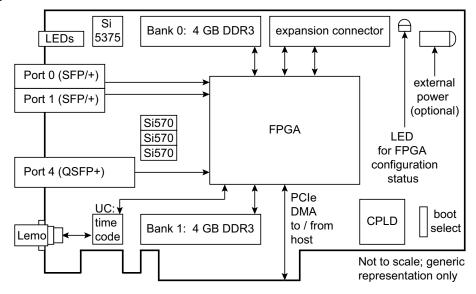

The S5 works as a standalone board. Block diagrams and ports for both versions (10G and 40G) are shown below.

## **Block Diagrams**

Figure 1 and Figure 2 show the respective architecture of the 10G version and the 40G version.

Figure 1. S5 10G

Figure 2. S5 40G

PCIe8g3 S5 Family Hardware

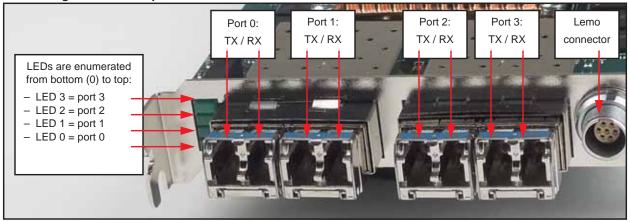

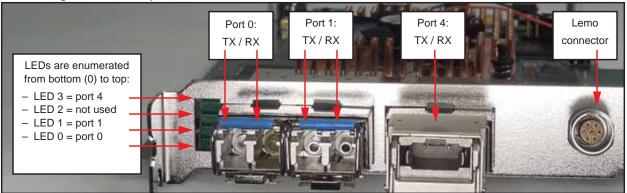

## **Ports and LED Status Indicators**

Figure 3 and Figure 4 show closeup images of the connectors and the LED status indicators.

Figure 3. S5 10G ports and LED status indicators

Figure 4. S5 40G ports and LED status indicators

Each LED indicates the status of its respective port – namely, whether the port is ready to receive, is receiving, and is framing a signal. If a port is working properly in all three areas, its LED is steady green. If not, its LED will be blinking.

Table 2 summarizes the LED behaviors.

Table 2. LED behaviors

| LED behavior    | FPGA receive clock locked / ready to receive? | Signal being received? | Signal being framed? |

|-----------------|-----------------------------------------------|------------------------|----------------------|

| Dim blinking    | No                                            | No                     | No                   |

| Bright blinking | Yes                                           | Yes                    | No                   |

| Bright steady   | Yes                                           | Yes                    | Yes                  |

## APPENDIX A: Registers for PCle8g3 S5

For the PCle8g3 S5 10G/40G, the registers are divided into two main categories and register spaces:

- the user interface (UI) register space, for functions that are not port-specific; and

- the port register space, for functions that are port-specific.

Each space contains both indirect and BAR1 memory-mapped registers, and the port register space is further divided so each port has its own indirect and BAR1 registers. The addresses are shown in Table 3.

Table 3. Addresses – UI and port registers (indirect and BAR1 memory-mapped)

|                                     | Indirect  | BAR1 memory-mapped |

|-------------------------------------|-----------|--------------------|

| UI registers<br>(non-port-specific) |           |                    |

| Any port                            | 0x00-0x7F | 0x000000-0x7FFFFF  |

| Port registers (port-specific)      |           |                    |

| Port 0                              | 0x80-0x87 | 0x800000-0x807FFF  |

| Port 1                              | 0x88-0x8F | 0x810000-0x817FFF  |

| Port 2                              | 0x90-0x97 | 0x820000-0x827FFF  |

| Port 3                              | 0x98-0x9F | 0x830000-0x837FFF  |

| Port 4                              | 0xA0-0xA7 | 0x840000-0x847FFF  |

The port registers are defined for port 0, and since each of the other ports has identical registers within its respective memory space, a C macro is included in edt\_stratix5.h to help you locate a specific register related to a specific port. The macro, which works for both indirect and BAR1 memory-mapped addresses, is defined as...

STRATIX5\_REGXL8(register\_address, port\_number)

...with the italicized variables being replaced by the appropriate register address and port number, as shown in the access information provided with each register below.

## Registers, UI

## 0x00-0x7F Indirect

### 0x00 Command

|     |        | Access / Notes: | 8-bit read-write / PCD_CMD                                                                                                                                                               |

|-----|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Access | Name            | Description                                                                                                                                                                              |

| 7–4 | RW     | PCD_STAT_INT_EN | Enables interrupts as defined in registers 0x03 Interrupt Status and 0x04 Interrupt Enable.                                                                                              |

| 3   | RW     | CMD_EN          | Set this bit to enable the required DMA channels in 0x10–11 DMA Channel Enable for DMA. When clear, resets all DMA channels, flushes all FIFOs, and clears all under- and overflow bits. |

| 2–0 | _      | -               | Reserved.                                                                                                                                                                                |

## 0x03 Interrupt Status

| UXU3 | interru | pt Status       |                                                                                                                                                                                                              |

|------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |         | Access / Notes: | 8-bit read-only / PCD_STAT                                                                                                                                                                                   |

|      |         |                 | This register is connected to 1Hz test interrupt as an example of interrupts generated by the UI FPGA on the main board.                                                                                     |

| Bit  | Access  | Name            | Description                                                                                                                                                                                                  |

| 7–4  | R only  | PCD_STAT_INT    | Interrupt bits for the status bits. If the corresponding bit is asserted in 0x00 Command, then the corresponding bit of these four can be asserted to cause a PCI bus interrupt.                             |

|      |         |                 | The PCI bus interrupt then is caused when the corresponding PCD_STAT signal [bits 3–0] is asserted. To reset the interrupt, disable and re-enable the appropriate PCD_STAT_INT_EN bit [7–4] in 0x00 Command. |

| 3–0  | R only  | PCD_STAT        | The state of user-definable STAT input signals as last sampled.                                                                                                                                              |

### 0x04 Interrupt Enable

|     |        | Access / Notes:      | 8-bit read-write / PCD_STAT_POLARITY                                                                                                                                                                                                                              |

|-----|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |                      | This register is connected to 1Hz test interrupt as an example of interrupts generated by the UI FPGA on the main board.                                                                                                                                          |

| Bit | Access | Name                 | Description                                                                                                                                                                                                                                                       |

| 7–5 | _      | _                    | Reserved.                                                                                                                                                                                                                                                         |

| 4   | RW     | PCD_STAT_INT_<br>ENA | Provides global enable or disable for all interrupt bits [7–4] in 0x03 Interrupt Status above, allowing the driver to disable and re-enable them in one operation without altering their states. A value of 1 enables the interrupts; a value of 0 disables them. |

| 3–0 | -      | [no name]            | Reserved.                                                                                                                                                                                                                                                         |

### 0x0D Exended Configuration

Access / Notes: 8-bit read-write / PCD\_EXT\_CONFIG

Registers 0x0D, 0x0F, and 0x16 all can affect how data is ordered.

BitAccessNameDescription7-1-[no name]Reserved.

RW WSWAP Word swap bit; swaps two 32-bit words in one 64-bit data word, so that word 0 is transferred before word

1. Does not change the position of the bits within each word.

### **0x0F** Configuration

Access / Notes: 8-bit read-write / PCD\_CONFIG

Registers 0x0D, 0x0F, and 0x16 all can affect how data is ordered.

BitAccessNameDescription7-4--Reserved.3RWSSWAPShort swap bit; swaps the two 16-bit short words in one 32-bit data word, so that short 0 is transferred before short 1. Does not change the order of the bits within each short.2-1--Reserved.0RWBSWAPByte swap bit; swaps bytes 0 and 1, and also bytes 2 and 3, in a 32-bit data word, so that the bytes are positioned 1, 0, 3, 2. Does not change the position of the bits within each byte.

Below is the structure of a 64-bit data word, with no swapping in effect.

Bits: 63-56 55-48 47–40 39–32 31–24 23-16 15-8 7-0 Bytes: 7 5 2 0 Shorts: 3 2 0 Words: 0

Below are the data ordering sequences achieved by setting or unsetting, in various combinations, the bits WSWAP, SSWAP, and BSWAP.

| WSWAP | SSWAP | BSWAP | Resultant Byte Order   |

|-------|-------|-------|------------------------|

| 0     | 0     | 0     | 7, 6, 5, 4, 3, 2, 1, 0 |

| 0     | 0     | 1     | 6, 7, 4, 5, 2, 3, 0, 1 |

| 0     | 1     | 1     | 4, 5, 6, 7, 0, 1 2, 3  |

| 1     | 1     | 1     | 0, 1, 2, 3, 4, 5, 6, 7 |

| 0     | 1     | 0     | 5, 4, 7, 6, 1, 0, 3, 2 |

| 1     | 0     | 0     | 3, 2 1, 0, 7, 6, 5, 4  |

#### 0x10-11 DMA Channel Enable

Access / Notes: 16-bit read-write / SSD16\_CHEN

Bit Access Name Description

15-0 RW CH\_ENABLE[15-0] Set or clear the appropriate bit to enable or reset the corresponding DMA channel:

Set bit 12 to transmit data to port 4; clear to reset.

Set bit 11 to transmit data to port 3; clear to reset.

Set bit 10 to transmit data to port 2; clear to reset.

Set bit 9 to transmit data to port 1; clear to reset.

Set bit 8 to transmit data to port 0; clear to reset.

Set bit 4 to receive data from port 4; clear to reset.

Set bit 3 to receive data from port 3; clear to reset.

Set bit 2 to receive data from port 2; clear to reset.

- Set bit 1 to receive data from port 1; clear to reset.

- Set bit 0 to receive data from port 0; clear to reset.

#### 0x16-17 Least Significant Bit First

Access / Notes: 16-bit read-write / SSD16\_LSB

Registers 0x0D, 0x0F, and 0x16 all can affect how data is ordered.

Bit Access Name Description

15-0 RW LSB\_FIRST[5-0] When set for a DMA channel, the least significant bit of the 32-bit data word is first, and the most

significant bit is last; when clear, the most significant bit of a 32-bit word is first.

#### 0x18-19 Underflow

Access / Notes: 16-bit read-only / SSD16\_UNDER

Bit Access Name Description

15-0 R only UNDERFLOW[12-0] A value of 1 in a bit indicates that the corresponding DMA channel's internal FIFO has underflowed

since the channel was last enabled. Underflow causes the corresponding DMA channel to transmit the last valid byte repeatedly until it receives new DMA data. To reset, clear and reenable the appropriate

channel (see 0x00 Command and 0x10-11 DMA Channel Enable).

#### 0x1A-1B Overflow

Access / Notes: 16-bit read-only / SSD16\_OVER

Bit Access Name Description

15–0 R only OVERFLOW[12–0] A value of 1 in a bit indicates that the corresponding DMA channel's internal FIFO has overflowed since

the channel was last enabled. Data received while the FIFO is in overflow is discarded. To reset, clear and reenable the appropriate channel (see 0x00 Command and 0x10–11 DMA Channel Enable).

#### 0x60-62 Extended Indirect Register Address

Access / Notes: 24-bit read-write / [no name]

0x60 = bits 7-0; 0x61 = bits 15-8; 0x62 = bits 23-16.

Bit Access Name Description

23-0 RW [no name] This is the register address space for the extended indirect registers.

#### 0x63 Extended Indirect Register Data

Access / Notes: 8-bit read-write / [no name]

Bit Access Name Description

7–0 RW [no name] This is the register data for the extended indirect registers.

- Writing this register writes data to the register addressed by 0x60-62.

- Reading this register reads the data addressed by 0x60-62.

#### 0x64 Serial Master Interface Status

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_DEVICE

| Bit | Access | Name                 | Description                                                       |

|-----|--------|----------------------|-------------------------------------------------------------------|

| 7   | R only | SER_DEV_BSY          | When set, the serial master is busy.                              |

| 6   | R only | SER_DEV_ACK_<br>FAIL | When set, the serial slave failed to respond to the last command. |

| 5-0 | RW     | SER_DEV_ADDR         | Descriptions for devices 0–20 are provided below.                 |

0 = Port 0 reference clock (Si570).

1 = Port 1 reference clock (Si570).

2 = Ports 2 and 4 reference clock (Si570).

3 = Port 3 reference clock (Si570).

4 = Port 0 external PLL (Si5375).

5 = Port 1 external PLL (Si5375).

6 = Port 2 external PLL (Si5375).

7 = Port 3 external PLL (Si5375).

8 = Port 0 SFP/+ EEPROM.

9 = Port 1 SFP/+ EEPROM.

10 = Port 2 SFP/+ EEPROM and Port 4 QSFP EEPROM.

11 = Port 3 SFP/+ EEPROM.

12 = Port 0 SFP/+ diagnostics.

13 = Port 1 SFP/+ diagnostics.

14 = Port 2 SFP/+ diagnostics.

15 = Port 3 SFP/+ diagnostics.

16 = Port 0 SFP active copper PHY.

17 = Port 1 SFP active copper PHY.

18 = Port 2 SFP active copper PHY.

19 = Port 3 SFP active copper PHY.

20 = U2M reference clock (Si5375).

#### 0x65 Serial Master Interface Read [7-0]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_READ\_ADDR

Bit Access Name Description

7-0 RW [no name] This register [bits 7-0] works with 0x68 Serial Master Interface Read [15-8].

Write the register address on the serial slave that you wish to read.

Read the data returned from the register address.

#### 0x66 Serial Master Interface Register Address [7–0]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_WRITE\_ADDR

Bit Access Name Description

7–0 RW [no name] This register [bits 7–0] works with 0x69 Serial Master Interface Register Address [15–8].

Write the register address on the serial slave that you wish to read.

Read the register address.

#### 0x67 Serial Master Interface Write [7-0]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_WRITE\_DATA

Bit Access Name Description

7–0 RW [no name] This register works [bits 7–0] with 0x6A Serial Master Interface Write [15–8].

Write data to the serial slave.

#### 0x68 Serial Master Interface Read [15-8]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_READ\_DATA\_UPPER

Bit Access Name Description

15–8 R only [no name] This register [bits 15–8] works with 0x65 Serial Master Interface Read [7–0].

Write the register address on the serial slave that you wish to read.

Read the data returned from the register address.

#### 0x69 Serial Master Interface Register Address [15–8]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_WRITE\_ADDR\_UPPER

Bit Access Name Description

15–8 RW [no name] This register [bits 15–8] works with 0x66 Serial Master Interface Register Address [7–0].

Write the register address on the serial slave that you wish to read.

Read the register address.

## 0x6A Serial Master Interface Write [15-8]

Access / Notes: 8-bit read-write / STRATIX5\_I2C\_WRITE\_DATA\_UPPER

Bit Access Name Description

15–8 RW [no name] This register [bits 15–8] works with 0x67 Serial Master Interface Write [7–0].

Write data to the serial slave.

#### 0x6B Reference Clock Control

Access / Notes: 8-bit read-write / STRATIX5\_EXT\_PLL

Bit

Access

Name

Description

7

RW

[no name]

Assert to reset the external PLL for all four interfaces.

6–4

Reserved.

3–0

RW

[no name]

Set to select the local reference crystal as the source forms.

Set to select the local reference crystal as the source for each respective interface on the external PLL;

otherwise, use the recovered clock as the source.

Bit 3 = Port 3 Bit 2 = Port 2 Bit 1 = Port 1 Bit 0 = Port 0

#### 0x6C Sync Trigger Control and Status

Access / Notes: 8-bit read-write / STRATIX5\_SYNC\_REG

Bit

Access

Name

Description

7-5

Reserved.

4

R only

STRATIX5\_SYNC\_ IN

Status of external synchronization trigger.

3-1

Reserved.

0

RW

STRATIX5\_SYNC\_ OUT

Set to send the synchronization trigger.

#### 0x6D SPI Data

Access / Notes: 8-bit read-write / SPI\_DATA

Bit Access Name Description

7–0 RW [no name] If read, bits read from the input FIFO.

If written, bits write to the output FIFO.

#### 0x6E SPI Status and Control

|     |        | Access / Notes:                       | 8-bit read-write / SPI_STAT_CTRL                                                                                                                               |

|-----|--------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Access | Name                                  | Description                                                                                                                                                    |

| 7   | R only | CHIP_ENABLE                           | Detects which main board is connected to the S5 master header. A value of 1 indicates the master header; otherwise reads 0.                                    |

| 6   | R only | IRIGB_PULSE_IN                        | If set, indicates that the 1 pps signal has been detected from the incoming IRIG signal, and has been processed by and passed through the microcontroller.     |

| 5   | R only | MODEM_PULSE_IN                        | If set, indicates that the 1 pps signal has been detected from the satellite modem and passed directly through, without any processing by the microcontroller. |

| 4   | _      | [no name]                             | Reserved; reads as 0.                                                                                                                                          |

| 3   | R only | FIFO_OUT_EMPTY                        | If set, indicates the output FIFO is empty.                                                                                                                    |

| 2   | R only | FIFO_OUT_FULL                         | If set, indicates the output FIFO is full.                                                                                                                     |

| 1   | R only | FIFO_IN_EMPTY                         | If set, indicates the input FIFO is empty.                                                                                                                     |

| 0   | RW     | If written: RESET If read: FIFO_IN_OV | On write: toggle this bit to reset the SPI data path. On read: when set, indicates the input FIFO has overflowed. Data may be lost.                            |

#### 0x6F SPI Strobe

Access / Notes: 8-bit write-only / SPI\_STROBE

Bit Access Name Description

7-0 W only [no name] Write (any value) to this register to advance the input FIFO.

#### 0x7C-7D FPGA Configuration File Design ID

Access / Notes: 16-bit read-only / PCD\_DESIGN\_ID

Bit Access Name Description

15–0 R only [no name] A 16-bit number assigned by the organization that produced the FPGA configuration file loaded in the

main board UI FPGA.

The design ID for pe8s5\_40g.bit is 0x1C00. The design ID for pe8s5\_4p.bit is 0x1C04.

### 0x7E FPGA Configuration File Version String

Access / Notes: 8-bit read-write / MAIN\_BITFILE\_VERSION

To read the FPGA configuration file version string from ROM, write the ROM address to the register and read the ASCII data from the same register. The version string is a maximum of 64 bytes long, so only

the first six bits of the address are significant.

Bit Access Name Description

7–0 RW ID\_ADD\_DATA Write an address to read ROM contents. Result is...

mainBoard\_mezzBoard\_bitfileName version.revision mm/dd/yyyy (number of DMA

channels used, number of DMA channels required by PCI FPGA)

mm/dd/yyyy is the date the FPGA configuration file was created. Replace italicized terms with actual

values — for example,  $sv16\_pe8s5\_4p$  0.0 04/24/2013 (10,10).

## 0x7F Board ID [Reserved]

## Registers, UI

## 0x000000-0x7FFFFF BAR1 Memory-Mapped

### 0x000010 Data Path and Memory Control

| oxedetic Bata i alli alla memery control |        |                            |                                                                                                                             |

|------------------------------------------|--------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                          |        | Access / Notes:            | 32-bit read-write / STRATIX5_MEMPATH_CTRL                                                                                   |

| Bit                                      | Access | Name                       | Description                                                                                                                 |

| 31–25                                    | _      | _                          | Reserved.                                                                                                                   |

| 24                                       | RW     | STRATIX5_MEM_<br>LOOP_MODE | Assert to enable loop mode to allow for looping in DDR3 memory. Use in conjunction with register 0x000024 Memory Loop Size. |

| 23-20                                    | RW     | [no name]                  | Select port (data source for memory).                                                                                       |

| 19–17                                    | _      | _                          | Reserved.                                                                                                                   |

| 16                                       | RW     | STRATIX5_SEL_<br>DMA       | Assert to direct data to DMA.                                                                                               |

| 15                                       | RW     | STRATIX5_MEM_<br>SYNC_DIMM | Assert to synchronize the DDR3 memory banks, effectively creating a single, wider bank of memory.                           |

| 14                                       | RW     | STRATIX5_MEM_<br>WR_FIRST  | Assert to set write priority for memory.                                                                                    |

| 13                                       | RW     | STRATIX5_MEM_<br>M1_ACTIVE | Memory port 1 active.                                                                                                       |

| 12                                       | RW     | STRATIX5_M0_<br>BYPASS     | Memory port 0 bypass mode.                                                                                                  |

| 11                                       | R only | [no name]                  | Bank D PHY initialization completed successfully.                                                                           |

| 10                                       | R only | [no name]                  | Bank C PHY initialization completed successfully.                                                                           |

| 9                                        | R only | [no name]                  | Bank B PHY initialization completed successfully.                                                                           |

| 8                                        | R only | [no name]                  | Bank A PHY initialization completed successfully.                                                                           |

| 7                                        | RW     | [no name]                  | Bank D logical reset.                                                                                                       |

| 6                                        | RW     | [no name]                  | Bank C logical reset.                                                                                                       |

| 5                                        | RW     | [no name]                  | Bank B logical reset.                                                                                                       |

| 4                                        | RW     | [no name]                  | Bank A logical reset.                                                                                                       |

| 3                                        | RW     | [no name]                  | Bank D PHY reset.                                                                                                           |

| 2                                        | RW     | [no name]                  | Bank C PHY reset.                                                                                                           |

| 1                                        | RW     | [no name]                  | Bank B PHY reset.                                                                                                           |

| 0                                        | RW     | [no name]                  | Bank A PHY reset.                                                                                                           |

### 0x000014 Memory Status

|       |        | Access / Notes: | 32-bit read-only / STRATIX5_DFIFO_STATUS |

|-------|--------|-----------------|------------------------------------------|

| Bit   | Access | Name            | Description                              |

| 31–28 | R only | [no name]       | Bank D debug information.                |

| 27–24 | R only | [no name]       | Bank C debug information.                |

| 23–20 | R only | [no name]       | Bank B debug information.                |

| 19–16 | R only | [no name]       | Bank A debug information.                |

| 15    | R only | [no name]       | Bank D 100% full.                        |

| 14 | R only | [no name] | Bank D 75% full.  |

|----|--------|-----------|-------------------|

| 13 | R only | [no name] | Bank D 50% full.  |

| 12 | R only | [no name] | Bank D 25% full.  |

| 11 | R only | [no name] | Bank C 100% full. |

| 10 | R only | [no name] | Bank C 75% full.  |

| 9  | R only | [no name] | Bank C 50% full.  |

| 8  | R only | [no name] | Bank C 25% full.  |

| 7  | R only | [no name] | Bank B 100% full. |

| 6  | R only | [no name] | Bank B 75% full.  |

| 5  | R only | [no name] | Bank B 50% full.  |

| 4  | R only | [no name] | Bank B 25% full.  |

| 3  | R only | [no name] | Bank A 100% full. |

| 2  | R only | [no name] | Bank A 75% full.  |

| 1  | R only | [no name] | Bank A 50% full.  |

| 0  | R only | [no name] | Bank A 25% full.  |

### 0x000018 W PRBS [Reserved]

### 0x00001C W PRBS 2 [Reserved]

#### 0x000024 Memory Loop Size

Access / Notes: 32-bit read-write / STRATIX5\_MEMLOOP\_LNGTH

BitAccessNameDescription31–0RW[no name]Memory loop size.

## 0x000028 Memory Information

Access / Notes: 32-bit read-only / STRATIX5\_MEMINFO

| Bit   | Access | Name      | Description                                                       |

|-------|--------|-----------|-------------------------------------------------------------------|

| 31–28 | _      | _         | Reserved.                                                         |

| 27–20 | R only | [no name] | Avalon address width, in bits.                                    |

| 19–10 | R only | [no name] | Data word width in bytes per bank.                                |

| 9–0   | R only | [no name] | Burst size in number of transfers (four data words per transfer). |

## Registers, Port: Ports 0-3 (SFPs)

### 0x80-0x9F Indirect

#### 0x80, 88, 90, 98 SFP Configuration and Status

Access / Notes: 8-bit read-write

0x80 (Port 0): STRATIX5\_REGXL8(STRATIX5\_OPT\_XCVR, 0) 0x88 (Port 1): STRATIX5\_REGXL8(STRATIX5\_OPT\_XCVR, 1) 0x90 (Port 2): STRATIX5\_REGXL8(STRATIX5\_OPT\_XCVR, 2) 0x98 (Port 3): STRATIX5\_REGXL8(STRATIX5\_OPT\_XCVR, 3)

| Bit | Access | Name      | Description                                              |

|-----|--------|-----------|----------------------------------------------------------|

| 7   | R only | [no name] | When set, indicates a loss of signal.                    |

| 6   | R only | [no name] | When set, indicates an SFP/+ transmit fault.             |

| 5   | R only | [no name] | When set, indicates the SFP/+ is connected and detected. |

| 4–3 | _      | _         | Reserved.                                                |

| 2   | RW     | [no name] | Set for SFP+ rate select (1).                            |

| 1   | RW     | [no name] | Set for SFP+ rate select (0).                            |

| 0   | RW     | [no name] | Set to disable transmit.                                 |

#### 0x82, 8A, 92, 9A Port Status

Access / Notes: 8-bit read-only

0x82 (Port 0): STRATIX5\_REGXL8(STRATIX5\_PORT\_STAT, 0) 0x8A (Port 1): STRATIX5\_REGXL8(STRATIX5\_PORT\_STAT, 1) 0x92 (Port 2): STRATIX5\_REGXL8(STRATIX5\_PORT\_STAT, 2) 0x9A (Port 3): STRATIX5\_REGXL8(STRATIX5\_PORT\_STAT, 3)

| Bit | Access | Name      | Description                                                           |

|-----|--------|-----------|-----------------------------------------------------------------------|

| 7   | _      | _         | Reserved.                                                             |

| 6   | R only | [no name] | When set, indicates the transceiver reconfiguration is in progress.   |

| 5   | _      | _         | Reserved.                                                             |

| 4   | R only | [no name] | When set, indicates the transceiver transmit PLL0 is locked.          |

| 3   | R only | [no name] | When set, indicates the transceiver CDR is locked to data.            |

| 2   | R only | [no name] | When set, indicates the transceiver CDR is locked to reference clock. |

| 1   | R only | [no name] | When set, indicates the transceiver is ready to receive.              |

| 0   | R only | [no name] | When set, indicates the transceiver is ready to transmit.             |

### 0x87, 8F, 97, 9F Port Information

Access / Notes: 8-bit read-only

0x87 (Port 0): STRATIX5\_REGXL8(STRATIX5\_PORT\_INFO, 0) 0x8F (Port 1): STRATIX5\_REGXL8(STRATIX5\_PORT\_INFO, 1) 0x97 (Port 2): STRATIX5\_REGXL8(STRATIX5\_PORT\_INFO, 2) 0x9F (Port 3): STRATIX5\_REGXL8(STRATIX5\_PORT\_INFO, 3)

| Bit Access Name Descrip | tion |

|-------------------------|------|

|-------------------------|------|

7–4 R only [no name] Port type (SFP+ = 0; QSFP = 1).

3–0 R only [no name] Port number.

## Registers, Port: Ports 0-3 (SFPs)

## 0x800000-0x837FFF BAR1 Memory-Mapped

#### 0x800000, 810000, 820000, 830000 Receive Framer Status and Control

| Access / Notes: | 32-bit read-write                                      |

|-----------------|--------------------------------------------------------|

|                 | 0x800000 (Port 0): STRATIX5_REGXL8(STRATIX5_RX_FRM, 0) |

|                 | 0x810000 (Port 1): STRATIX5_REGXL8(STRATIX5_RX_FRM, 1) |

|                 | 0x820000 (Port 2): STRATIX5_REGXL8(STRATIX5_RX_FRM, 2) |

0x820000 (Port 2): STRATIX5\_REGXL8(STRATIX5\_RX\_FRM, 2) 0x830000 (Port 3): STRATIX5\_REGXL8(STRATIX5\_RX\_FRM, 3)

|       |        |                         | 0x030000 (F0It 3). 31KA1IX3_KEGXE0(31KA1IX3_KX_1 KW, 3)                                                                   |

|-------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Bit   | Access | Name                    | Description                                                                                                               |

| 31    | R only | [no name]               | Copy of S5_RXFRM_BYTE_ALGND.                                                                                              |

| 30–28 | R only | [no name]               | Byte offset.                                                                                                              |

| 27    | R only | [no name]               | Copy of S5_RXFRM_BIT_ALGND.                                                                                               |

| 26–24 | R only | [no name]               | Bit offset.                                                                                                               |

| 23–16 | _      | _                       | Reserved.                                                                                                                 |

| 15    | R only | S5_RXFRM_FRM_<br>LCKD   | When set, the framer has detected multiple consecutive frames and is locked.                                              |

| 14    | R only | S5_RXFRM_FRM_<br>FOUND  | When set, the framer has deteced the beginning of an SDH / OTN frame.                                                     |

| 13–10 | _      | _                       | Reserved.                                                                                                                 |

| 9     | R only | S5_RXFRM_BYTE_<br>ALGND | When set, the framer is byte-aligned to the SDH / OTN frame alignment signal (FAS) pattern.                               |

| 8     | R only | S5_RXFRM_BIT_<br>ALGND  | When set, the framer is bit-aligned to the SDH / OTN frame alignment signal (FAS) pattern.                                |

| 7–5   | _      | _                       | Reserved.                                                                                                                 |

| 4     | RW     | S5_RXFRM_DIS_<br>DSCRM  | Set to disable the descrambler (i.e., acquire framed, scrambled data). Used only in conjunction with bit 1 (S5_RXFRM_EN). |

| 3     | RW     | S5_RXFRM_CHK_<br>PAYLD  | Set to enable hardware checking of PRBS payload data.                                                                     |

| 2     | RW     | S5_RXFRM_CAT_<br>PAYLD  | Set to capture only payload data (i.e., strip framing).                                                                   |

| 1     | RW     | S5_RXFRM_EN             | Set to allow data acquisition only when the framer is locked to the incoming signal. Acquired data is descrambled.        |

| 0     | RW     | S5_RXFRM_RST            | Reset framer. Set, then clear to force the framer to drop, then relock onto the framing pattern.                          |

|       |        |                         |                                                                                                                           |

#### 0x800004, 810004, 820004, 830004 Receive Filter

Access / Notes: 32-bit read-write

0x800004 (Port 0): STRATIX5\_REGXL8(STRATIX5\_RX\_FILTER, 0) 0x810004 (Port 1): STRATIX5\_REGXL8(STRATIX5\_RX\_FILTER, 1) 0x820004 (Port 2): STRATIX5\_REGXL8(STRATIX5\_RX\_FILTER, 2) 0x830004 (Port 3): STRATIX5\_REGXL8(STRATIX5\_RX\_FILTER, 3)

| Bit  | Access | Name                        | Description                                                            |

|------|--------|-----------------------------|------------------------------------------------------------------------|

| 31–8 | _      | _                           | Reserved.                                                              |

| 7    | RW     | S5_RXFILT_IGNR_<br>ALL_FILT | Set to ignore all filters (overrides all other bits in this register). |

| 6–3 | -  | _                           | Reserved.                                                            |

|-----|----|-----------------------------|----------------------------------------------------------------------|

| 2   | RW | S5_RXFILT_STRIP_<br>FEC     | Set to strip FEC (OTU only).                                         |

| 1   | RW | S5_RXFILT_ALL_<br>OTU_OVRHD | Set to force capture of OTU overhead (regardless of the demux mask). |

| 0   | RW | S5_RXFILT_<br>OVRHD_ONLY    | Set to capture only frame overhead data (i.e., strip payload).       |

#### 0x800008, 810008, 820008, 830008 Transmit Framer Control [Reserved]

#### 0x80000C, 81000C, 82000C, 83000C Line Rate / Protocol Control

Access / Notes: 32-bit read-write

0x80000C (Port 0): STRATIX5\_REGXL8(STRATIX5\_PORT\_RATE, 0)

0x81000C (Port 1): STRATIX5\_REGXL8(STRATIX5\_PORT\_RATE, 1)

0x82000C (Port 2): STRATIX5\_REGXL8(STRATIX5\_PORT\_RATE, 2)

0x83000C (Port 3): STRATIX5\_REGXL8(STRATIX5\_PORT\_RATE, 3)

BitAccessNameDescription31–8--Reserved.

7–0 RW [no name] Set expected line rate / protocol:

0 = STM64 / OC192 1 = STM16 / OC48 2 = STM4 / OC12 3 = STM1 / OC3 4 = 1GbE 5 = 10GbE 6 = OTU2 7 = OTU2e 8 = OTU2F 9 = OTU1

#### 0x800010, 810010, 820010, 830010 Synchronization Control

Access / Notes: 32-bit read-write

0x800010 (Port 0): STRATIX5\_REGXL8(STRATIX5\_PSYNC\_CTRL, 0)

0x810010 (Port 1): STRATIX5\_REGXL8(STRATIX5\_PSYNC\_CTRL, 1)

0x820010 (Port 2): STRATIX5\_REGXL8(STRATIX5\_PSYNC\_CTRL, 2)

0x830010 (Port 3): STRATIX5\_REGXL8(STRATIX5\_PSYNC\_CTRL, 3)

| Bit   | Access | Name                    | Description                                                                                                                                                                                                             |

|-------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–16 | _      | _                       | Reserved.                                                                                                                                                                                                               |

| 15    | RW     | STRATIX5_<br>TXTRIG_ARM | Set to arm transmit trigger.                                                                                                                                                                                            |

| 14    | _      | _                       | Reserved.                                                                                                                                                                                                               |

| 13–12 | RW     | [no name]               | Select when DDR3 FIFO transmit will start:  0 = ignore  1 = when FIFO is 50% full  2 = when FIFO is 75% full  3 = when FIFO is 100% full  The transmit logic waits to transmit until the selected threshold is reached. |

| 11–10 | _      | _                       | Reserved.                                                                                                                                                                                                               |

| 9–8 | RW | [no name]               | Select transmit trigger source: 0 = external 1 = internal |

|-----|----|-------------------------|-----------------------------------------------------------|

| 7   | RW | STRATIX5_<br>RXTRIG_ARM | Set to arm receive trigger.                               |

| 6–3 | _  | _                       | Reserved.                                                 |

| 2   | RW | [no name]               | Set to disable wait for frame receive trigger mode.       |

| 1–0 | RW | [no name]               | Select receive trigger source: 0 = external 1 = internal  |

#### 0x800014, 810014, 820014, 830014 Frame Statistics Count Control

Access / Notes: 32-bit read-write

0x800014 (Port 0): STRATIX5\_REGXL8(STRATIX5\_FRM\_CNT\_CTRL, 0) 0x810014 (Port 1): STRATIX5\_REGXL8(STRATIX5\_FRM\_CNT\_CTRL, 1) 0x820014 (Port 2): STRATIX5\_REGXL8(STRATIX5\_FRM\_CNT\_CTRL, 2) 0x830014 (Port 3): STRATIX5\_REGXL8(STRATIX5\_FRM\_CNT\_CTRL, 3)

| 31–8 | _  | _         | Reserved.                                                                                              |

|------|----|-----------|--------------------------------------------------------------------------------------------------------|

| 7    | RW | [no name] | Set to enable the frame statistics counters; clear to reset the counters.                              |

| 6–1  | _  | _         | Reserved.                                                                                              |

| 0    | RW | [no name] | Set to capture frame statistics counter data (B1, B2, M1, LOF); clear to update counters continuously. |