# **Liquid-Cooled** with **300A** Power Supply

**XUPVVP**PCle FPGA Board

## **Power Edition for Monster FPGA Loads**

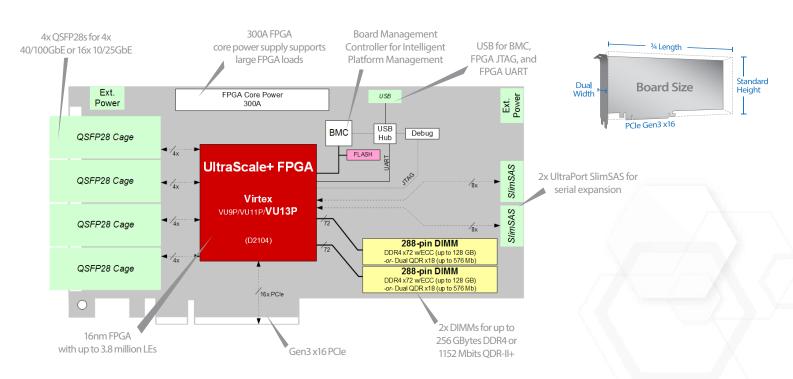

BittWare's XUPVVP is an UltraScale+ VU13P FPGA-based PCIe card, designed for ultra high power applications. The Xilinx UltraScale+ VU13P FPGA gives designers incredible performance potential, with 3.8M logic elements —yet with a power density that makes power and thermal management difficult. The XUPVVP meets this challenge with BittWare's Viper platform, supporting monster FPGA loads, up to 256 GBytes DDR4 or 1152 Mbits QDR-II+, and 4x 100 Gbps Ethernet.

BittWare's Viper platform uses advanced computer flow simulation to drive the physical board design in a thermals first approach, including the use of heat pipes, airflow channels, and arranging components to maximize the limited available airflow in a server. While the default option for the board is air-cooling, the XUPVVP is also available with liquid cooling for rapid heat removal. A 300A FPGA core power supply powers even the largest FPGA loads.

Xilinx VU13P FPGA: lidless package is used by BittWare's Viper thermal management for enhanced cooling performance

## key features

**300A**FPGA core power supply

Viper platform **Liquid Cooling** option for extreme FPGA loads Up to VU13P FPGA: **3.8 million LCs 360Mb UltraRAM** FPGA by Xilinx

## **XUPVVP**

PCle FPGA Board

#### **High-Speed Networking and I/O**

The XUPVVP is enabled for high-speed networking with four front panel QSFP+ cages, each supporting 40/100GbE or four 10/25GbE channels. Serial expansion is available through two UltraPort SlimSAS connectors (16x 25Gbps) that can be connected to a second PCle interface, another XUPVVP, or other devices, including IBM's POWER9 via OpenCAPI. A USB interface is provided for debug and programming support.

#### **System Management**

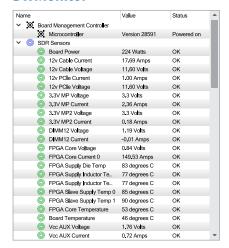

For system management, the XUPVVP is equipped with a Board Management Controller (BMC), which accepts IPMI 2.0 commands. Use it along with BittWare's BittWorks II Toolkit to program the FPGA Flash over USB, monitor board power and temperature, re-program the onboard clocks, and adjust FPGA core voltage. The BMC monitors critical temperatures, voltages, and current and will shut the board down to prevent damage. Recovery from shutdown is also supported, without the need to cycle system power.

#### **BittWorks II Toolkit**

BittWare offers complete software support for the XUPVVP with its BittWorks II software tools. The BittWorks II Toolkit is a suite of development tools that serves as the main interface between the BittWare board and the host system. The Toolkit includes drivers, libraries, utilities, and example projects for accessing, integrating, and developing applications for the BittWare board.

#### **FPGA Examples**

BittWare provides FPGA board support IP to simplify integration and development. These example projects illustrate how to move data between the board's different interfaces and are designed to integrate easily with the Xilinx Vivado tools. All examples are available for download on BittWare's developer website.

#### **BWMonitor**

Live board power/temperature display is included as part of Toolkit Lite

### **Board Specifications**

| FPGA                    | <ul> <li>Virtex UltraScale+ VU9P/VU11P/VU13P</li> <li>48x GTY transceivers at 32.75 Gbps</li> <li>Up to 3.8 million logic elements</li> <li>Over 400 Mb of embedded memory</li> <li>Up to 6 integrated PCle cores</li> <li>Up to 11,904 DSP slices with 27x18 multipliers</li> </ul> |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-board memory         | Flash memory for booting FPGA                                                                                                                                                                                                                                                        |

| Optional DIMM<br>memory | <ul> <li>2 DIMM sites, each supporting<sup>†</sup>:</li> <li>Up to 128 GBytes DDR4 x72 with ECC</li> <li>Up to 576 Mbits dual QDR-II+ x18 (2 independent 288 Mbit banks)</li> </ul>                                                                                                  |

| PCIe interface          | x16 Gen1, Gen2, Gen3 interface direct to FPGA (optional; no power used from PCIe connector)                                                                                                                                                                                          |

| Utility header          | USB, 1 PPS input, 1GbE                                                                                                                                                                                                                                                               |

| UltraPort SlimSAS       | <ul> <li>2 UltraPort SlimSAS on rear edge connected to<br/>FPGA via 16x GTY transceivers</li> <li>Provides 400Gbps board-to-board bandwidth</li> <li>Can support an additional x16 or x8 PCle interface<br/>(requires soft IP core and additional slot)</li> </ul>                   |

| QSFP cages              | <ul> <li>4 QSFP28 (zQSFP) cages on front panel connected directly to FPGA via 16 transceivers</li> <li>Each supports 100GbE, 40GbE, 4x 25GbE, or 4x 10GbE and can be combined for 400GbE</li> <li>Provides 400Gbps board-to-board bandwidth</li> </ul>                               |

| Board<br>Management<br>Controller | <ul> <li>Voltage, current, temperature monitoring</li> <li>Power sequencing and reset</li> <li>Field upgrades</li> <li>FPGA configuration and control</li> <li>Clock configuration</li> <li>I<sup>2</sup>C bus access</li> <li>USB 2.0</li> <li>Voltage overrides</li> </ul> |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power & cooling                   | <ul> <li>Liquid-cooled or air-cooled</li> <li>Dual external 8-pin power connectors<br/>(both must be connected)</li> <li>300A FPGA core power supply</li> </ul>                                                                                                              |

| Size                              | <ul> <li>¾-length, standard-height PCle dual-slot card</li> <li>254mm x 111.15mm</li> <li>Max. component height: 34.79mm dual slot</li> </ul>                                                                                                                                |

## **Development Tools**

| System development | BittWorks Il Toolkit - host, command, and debug tools for BittWare hardware                              |

|--------------------|----------------------------------------------------------------------------------------------------------|

| FPGA development   | <ul> <li>FPGA Examples - example Vivado projects</li> <li>Xilinx Tools - Vivado® Design Suite</li> </ul> |

## **XUPVVP Ordering Options**

| Ruggedization<br>0U = Commercial (0°C to 50°C)                         | FF | FF DIMM 2‡  00 = None*  R4 = DDR4 16GB RDIMM  R5 = DDR4 32GB RDIMM  R7 = DDR4 128GB RDIMM  L5 = DDR4 32GB LRDIMM  L6 = DDR4 64GB LRDIMM  L7 = DDR4 128GB LRDIMM  Q5 = QDRII+ x18 576 Mb (dual 288Mb) | L | SlimSAS<br>0 = Installed*                 |

|------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------|

| UltraScale Printed Wiring Board G = Optimized for VU13P*               |    |                                                                                                                                                                                                      | M | Factory JTAG Header<br>0 = Not Installed* |

| B FPGA Type and Size<br>13VP = Virtex VU13P*                           |    |                                                                                                                                                                                                      | N | 1 = Installed  USB-to-JTAG 1 = Installed* |

| FPGA Core Speed Grade<br>1 = Slower                                    |    |                                                                                                                                                                                                      | 0 | Heatsink                                  |

| 2 = Standard*<br>3 = Faster                                            | G  | Oscillator<br>S = Standard*                                                                                                                                                                          |   | 2 = Passive * L = Liquid cooling          |

| FPGA Temperature Range<br>E = Extended (Tj = 0 to +100C)*              | Н  | Clock Generator A<br>0 = 322.265625 MHz*                                                                                                                                                             | Р | Mechanical Options 0 = Default*           |

| DIMM 1‡ 00 = None* R4 = DDR4 16GB RDIMM                                | I  | Clock Generator B<br>0 = 322.265625 MHz*                                                                                                                                                             | Q | eFuse<br>0 = None*                        |

| R5 = DDR4 32GB RDIMM<br>R7 = DDR4 128GB RDIMM<br>L5 = DDR4 32GB LRDIMM | J  | Timing<br>0 = None*                                                                                                                                                                                  | R | Misc. Configuration<br>0 = Default        |

| L6 = DDR4 64GB LRDIMM<br>L7 = DDR4 128GB LRDIMM                        | K  | QSFP Configuration<br>4 = 4 QSFP cages*                                                                                                                                                              | S | Assembly<br>6 = RoHS 6/6                  |

<sup>\*</sup> Default

$<sup>\</sup>dagger$  Contact BittWare for availability

$<sup>\</sup>ddagger$  DIMM sites 1/2 must have the same memory type, or be empty.