Gidel FPGA ProcDev Dev Kit inklusive ProcWizard | Gidel FPGA IP Cores | Gidel I ++ HLS-Anwendungsunterstützung

Gidel ProcDev FPGA Development Kit einschließlich ProcWizard

Das Gidel Proc Developer's Kit (ProcDev Kit) ist ein leicht zu verwendendes FPGA-Designtool. Es optimiert den integrierten Speicher und die Hostkommunikation zur Unterstützung Ihrer Algorithmusimplementierung auf dem FPGA.

Das Developer-Kit enthält die ProcWizard-Anwendung, eine API, Gidel-IPs, Beispiele sowie HDL- und Software-Bibliotheken.

ProcWizard Rapid FPGA-Anwendungsentwicklungstool

Der Gidel ProcWizard ™ ist ein Hardware-Software-Integrationstool, das die FPGA-Projektentwicklung vereinfacht. ProcWizard ermöglicht den schnellen Entwurf von Anwendungen, die auf Gidel-FPGA-Karten auszuführen sind.

Das Design wird automatisch in HDL- und C++ - Code übersetzt. Der generierte HDL- und C++ - Code kommunizieren über den PCIe-Bus, um die Integration von Hardware und Software zu vereinfachen.

ProcWizard kann auch zum Testen und Debuggen von Designs auf dem PC verwendet werden. Im Debug-Modus kann über einen Strukturinspektor manuell oder mithilfe von Makros und Skripten auf die Gidel-FPGA-Karte „Proc“ zugegriffen werden.

Hardware- und Software-Designer können mit denselben Informationen und Projektdefinitionen zusammenarbeiten. Durch die parallele Arbeit in der gemeinsam genutzten Umgebung von Gidel ProcWizard wird die Entwicklungszeit verkürzt, die Zuverlässigkeit des Produkts erhöht und die Wartbarkeit verbessert.

- Zu den Hauptfunktionen von ProcWizard gehören:

- Automatische Integration von Software und Gidel-FPGA-Boards der Proc-Serie

- Automatische Integration der IP-Cores von Gidel in das Design

- Generierung von Anwendungstreibern der C++ - Klasse

- HDL-Code-Generierung (Top-Level-Design, PCI-Interface-Sub-Design, Board-Einschränkungen)

- Dokumentationserstellung (HTML oder Microsoft Word-Stil)

- Zertifizierung der Partitionsgenerierung

- Einfache, benutzerfreundliche, Menugesteuerte Oberfläche

- Automatische Hardware-Initialisierung und Uhreinstellung

- Automatisches Laden des FPGA

- Automatische DMA-Manipulationen

- Hardware-Debugging

Gidel FPGA IP-Cores für Intellectual Property

Das Gidel „ProcDev“ Developer-Kit enthält eine Reihe von IP-Cores zur Vereinfachung und Verbesserung der Entwicklungsaufgaben.

MultiPort FPGA IP Core

Der Gidel MultiPort IP ist ein Speichercontroller, der den integrierten Speicher gemäß den Anforderungen des Anwendungsdatenflusses optimiert. Dieser Controller ermöglicht den parallelen Zugriff von bis zu 16 unabhängigen Ports pro Speicherbank. Jeder Port kann zu einem separaten logischen Speicher gehören. Alle Ports sind mit derselben Speicherdomäne verbunden und können unabhängig oder gleichzeitig mit einzelnen Taktdomänen und Datenbreiten angesprochen werden.

MegaFIFO FPGA IP Core

Das MegaFIFO ermöglicht eine einfache und bequeme Datenübertragung zwischen den Speicherbänken der FPGA-Karte und der FPGA-Logik und / oder dem PC-Host.

MegaDelay FPGA IP Core

Das MegaDelay IP ermöglicht Verzögerungen mit hoher Bandbreite, um Streaming-Anwendungen zu optimieren. Diese IP-Adresse kann die Speicherzugriffsanforderungen in Kombination mit dem internen Speicher und der Logik des FPGA erheblich verringern.

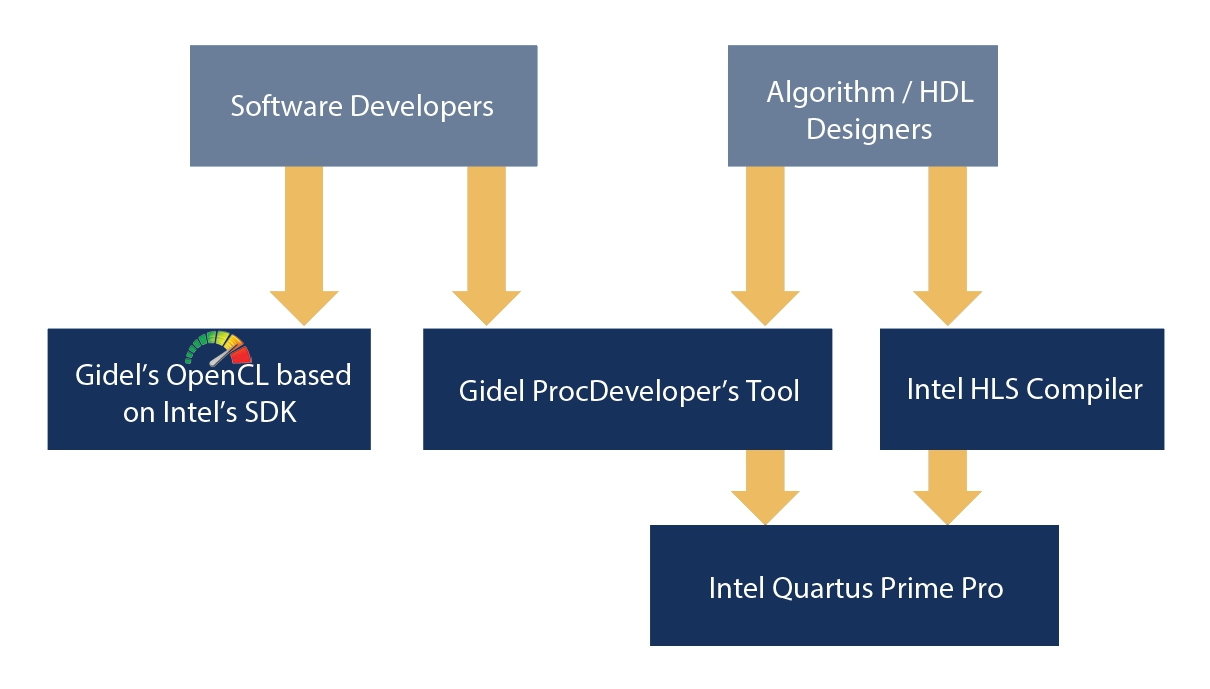

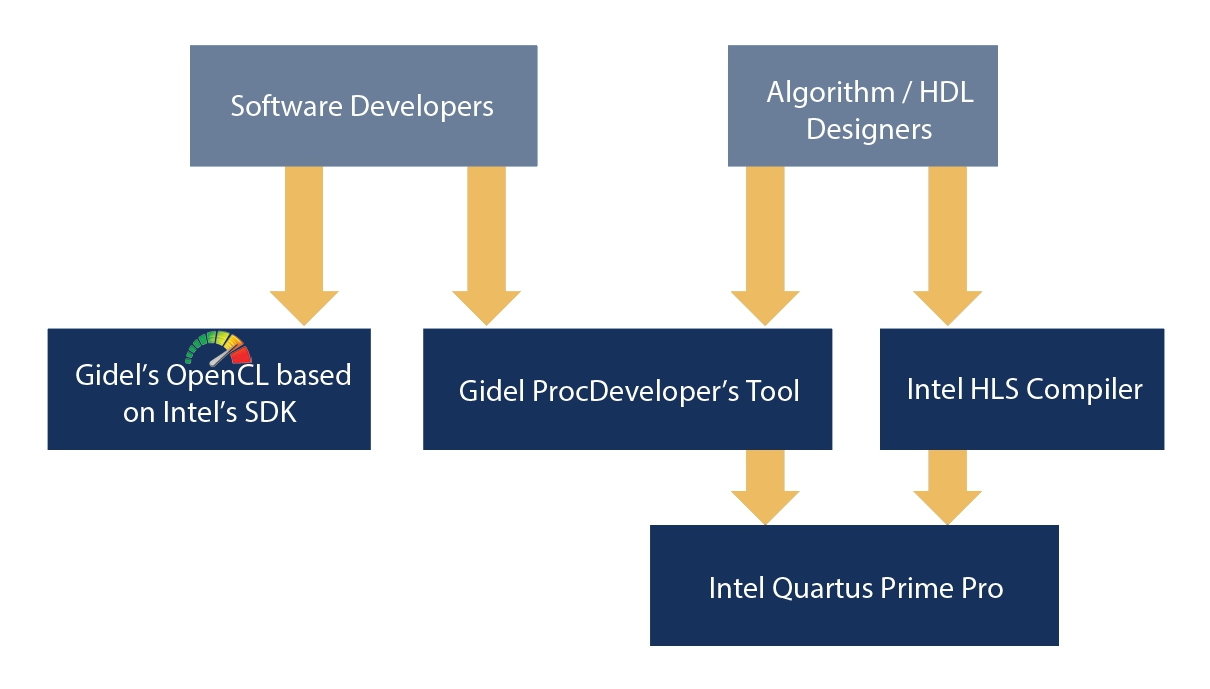

Gidel I ++ HLS-Anwendungsunterstützungspaket

Das HLS Application Support Package (I ++) ermöglicht die Verwendung des Intel High Level Synthesis (HLS) -Tools, das C++ als Eingabe verwendet und FPGA-optimierte Register Transfer Level (RTL) generiert. Die signifikante Code-Reduzierung kurzt die RTL-Überprüfungszeit.

Produktdaten